Hello,

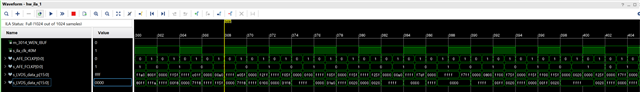

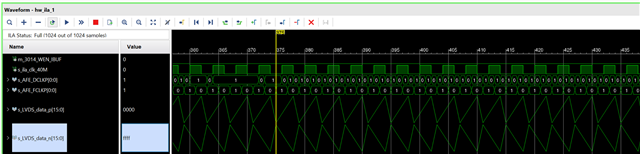

I attempted to verify the LVDS timing through the test pattern of the AFE5816 device, but when checked using Vivado's ILA, it was found that it did not appear correctly. Upon further inspection, it was discovered that the DCLK was not functioning properly. The ADC clock input to the AFE was confirmed to be a 40MHz differential clock, operating correctly, and the FCLK was also confirmed to output correctly at 40MHz. The image below is the result of checking the ramp test pattern through ILA. Given the 12-bit serialization factor and 12-bit quantization, I expected the frequency to be 6 times that of the FCLK, but it was confirmed that it did not appear correctly. It was also confirmed that it does not operate correctly on the board as well. Could there be a reason why only the DCLK is not working? I would appreciate your response.