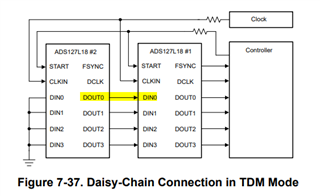

It is difficult to me from the datasheet to find out how many devices can be daisy-chained.

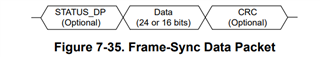

I want to use a one-bit stream to an FPGA.

I want to daisy-chain 8 devices for 64 channels.

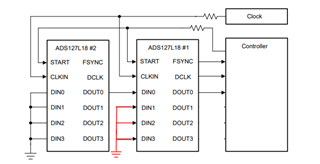

The "tc (DCLK) period DOUT to DIN daisy-chain connection " is spec'd as 29.8 nS .

Does it mean I need a tc (DCLK) period of 8x 29.8 = 238.4 nS (4.19 MHz)?