Hello everyone,

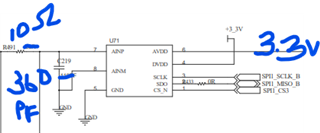

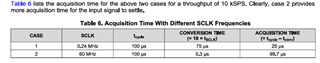

I am currently working on the ADS7046 ADC and an STM32H745 microcontroller. However, I am facing challenges regarding accurate waveform sampling via SPI. My objective is to sample a waveform with a frequency of up to 2MHz. Here are the details of my setup and the challenges I am encountering:

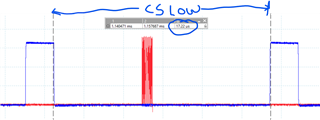

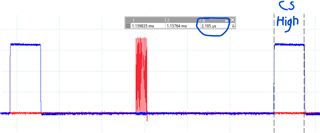

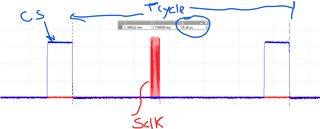

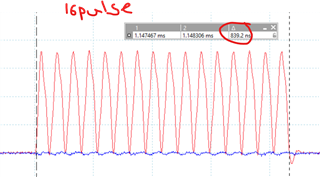

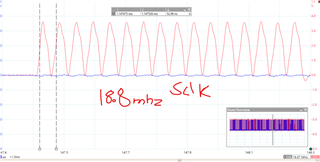

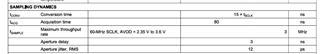

Current Setup: I have configured SPI communication between the ADS7046 and STM32H745. Presently, I am utilizing a 16-clock pulse with an SPI clock frequency (SCLK) of 18 MHz.

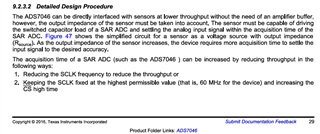

Challenges: Despite setting up SPI communication, I am experiencing difficulties in accurately sampling the input waveform. Specifically, I am uncertain about the appropriate SCLK frequency and the chip select (CS) on/off timings required to achieve reliable sampling at frequencies up to 1 MHz.

Please suggest the number of clock pulses and the SCLK frequency required to properly sample high-speed waveforms. Additionally, any recommendations regarding hardware requirements, such as RC filter values, would be greatly appreciated.

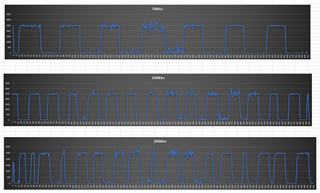

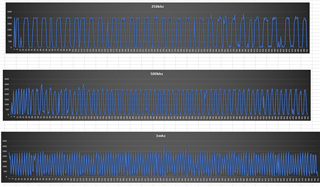

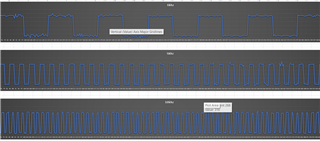

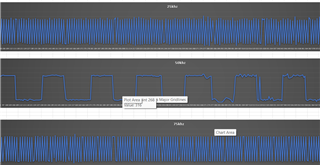

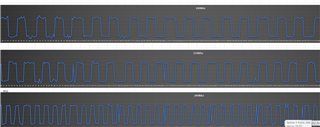

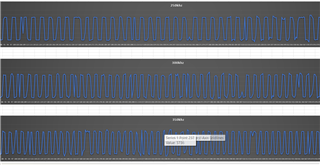

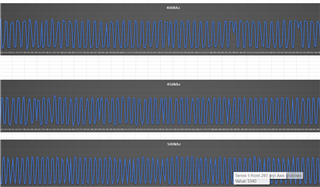

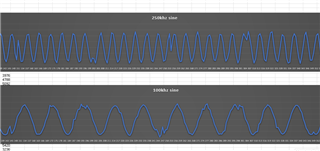

I have attached some snapshots of the results below.

Here, I have provided some input square and sine pulses from a function generator to the ADC. I have observed that sampling works well at frequencies of 50 kHz and below, such as for 100 Hz, 1 kHz, 5 kHz, 50 kHz, 100 kHz, 150 kHz, 200 kHz, and 250 kHz, up to 500 kHz. However, I am encountering issues with other frequencies, such as 10 kHz, 20 kHz, 25 kHz, 90 kHz, 125 kHz, etc. Could you please assist in identifying the problem?

Thank you for your attention and assistance.

attach some result of measurement.

attach some result of measurement.