Other Parts Discussed in Thread: TI-JESD204-IP,

Hi,

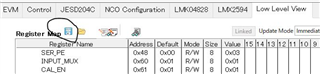

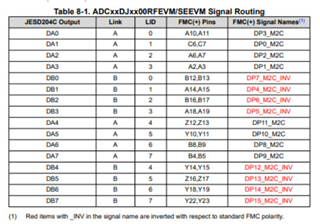

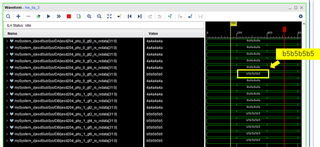

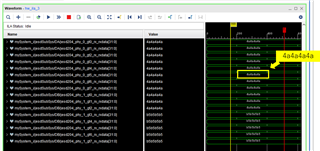

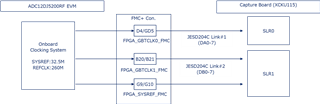

When communicating with JESD204B using JMODE1 (2 links, 16 lanes), the rx_start_of_frame values of two JESD204 PHY IPs are out of phase. Is this a reasonable guess?

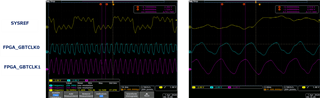

GBTCLK0 and GBTCLK1 are out of phase

The frame timing of the two links (DA, DB) appears to be out of sync.

GBTCLK0 and GBTCLK1 are used for convenience on the FPGA side.

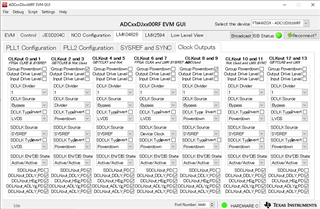

GBTCLK1 was default output OFF.

Is it possible to turn on GBTCLK1 by default?

Regards,

Takeo