Part Number: ADC3663

Hi team,

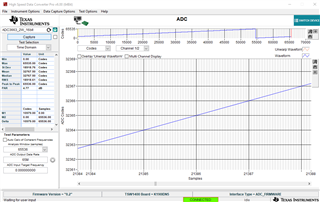

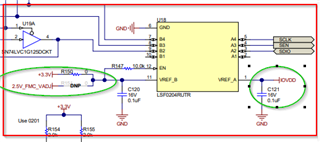

Use ADC3663 with 2-wire mode, 16bit output. There are some problems:

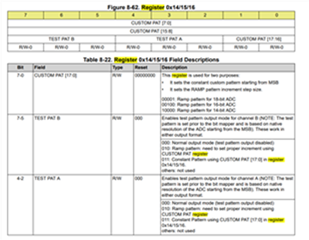

1.How to configure below three registers to output an increasing sequence, with a difference of 1 between each number?

2.What is the function of bit mapper?

3.The SPI interface between the ADC3663 and the FPGA uses a level translation chip(TS0108E-Q1/TSB0108), but the high and low levels of the chip are not normal, and it feels like it is caused by the pull-down resistance inside the ADC3663 SPI pins. If you have any comments about this problem? Thanks.