Other Parts Discussed in Thread: DAC39RF10-SP, , AFE7950-SP, DAC39RF10, ADC12DJ5200RF, AFE7950, TSW14J58EVM

Hi,

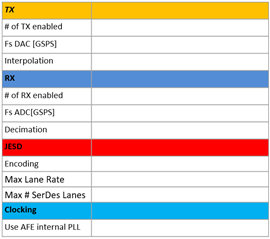

Customer would like to adopt ADC12DJ5200-SP and DAC39RF10-SP with Polarfire for supporting C-band, X-band.

Is it available in JESD interface?

When customer checked AFE7950-SP with Polarfire, it's not available due to JESD lane speed because Polarfire's interface speed is low.

Thanks.