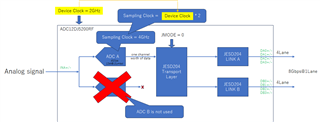

Is the device clock A)4GHz under the following conditions? Or is it B)2GHz?

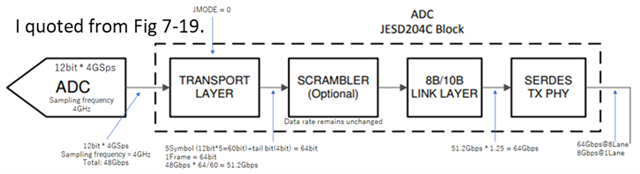

For example, I want to transmit 12 bits of data per symbol at 4GSps.

The sampling frequency is 4GHz.

A) At this time, 4 tail bits are added to 5 symbols (60 bits) in the transport layer,

Considering 8b/10b conversion, 48Gbps * 64/60 * 1.25 = 64Gbps

When transmitting with 8 lanes, the data rate is 8 Gbps per lane (lane_rate)

When JMODE = 0, it operates in single channel mode and the sampling rate is twice the device clock, so

I calculated that the device clock would be 4GHz.

But, I can think differently.

B) glbl_clk = lane_rate / 40 = 200MHz

device clock = sample_rate / 2 = 2GHz