Tool/software:

Dear Technical Support Team,

Is it possible to use dual channel mode (register 0x201 =3 ) on the ADC12DJ3200 to shift and adjust the sampling timing of the two ADCs between ADC INA and ADC INB?

Q1

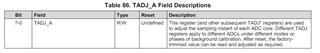

Are TADJ_A (0x086) and TADJ_B (0x089) correct for the sampling timing adjustment registers?

If not, please let us know the appropriate register.

Q2

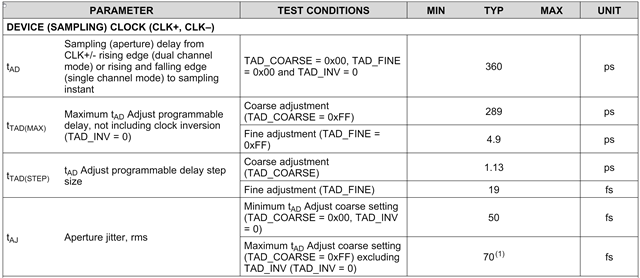

How many CLK cycles or how many seconds can the sampling timing be shifted ?

I didn't find this on the 0x86,0x89 register page

Q3

Is there a setting order specification, before CAL_EN (0x061) or in a different order?

Is there a specified order of settings?

There is a general setup procedure in 8.3 Initialization Set Up,

What steps should be taken to set registers to adjust sampling timing?

...

Best Regards,

ttd