Tool/software:

Hello,

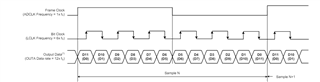

I am integrating the ADS5296A into my design with a 160 MHz input clock and am trying to generate a 12-bit Ramp Test Pattern. Unfortunately, I am not seeing any output from the ADC, and the interleaved mode is enabled in my setup.

I have a few concerns and would greatly appreciate your guidance on the following:

1. What should the frame clock rate be? Should it match the input clock or be half of it? When I probe the clock, it is unstable, varying from 65 MHz to 80 MHz.

2. Could you please confirm the specific registers I need to configure to initiate the Ramp test pattern? Is there a specific sequence of writes I need to follow? Below are the register writes I have attempted:

- 00h: 0001h

- 00h: 0000h

- 07h: 0001h

- 40h: 8000h

- 45h: 0000h

- 46h: 8208h

- 25h: 0140h

Thank you for your assistance.

Best regards,

Akshit