Part Number: ADS7038-Q1

Tool/software:

Hello,

i have trouble to get the averaging working. I've tried in manual and auto-sequence mode. The OSR_DONE bit never changes to one. In the following i show you my attempt with 2 samples averaging and manual mode.

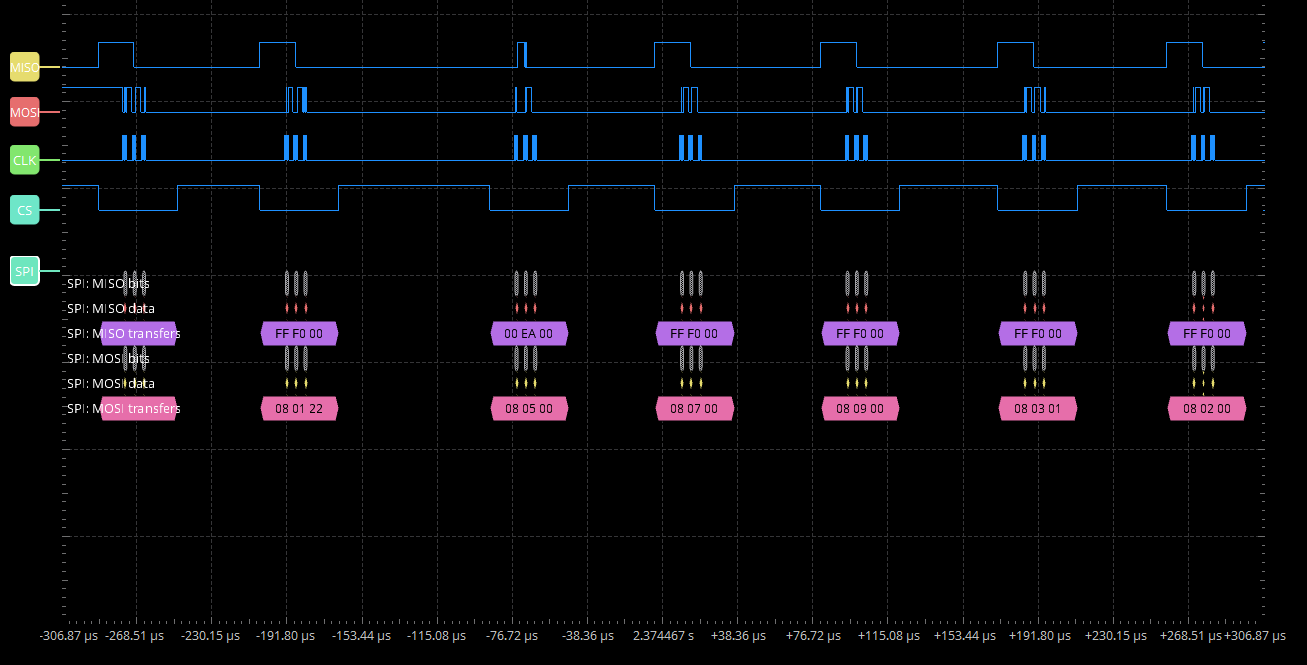

First the ADS 7038 config after start up (first clear BOR bit, then everything zero except the OSR_CFG register):

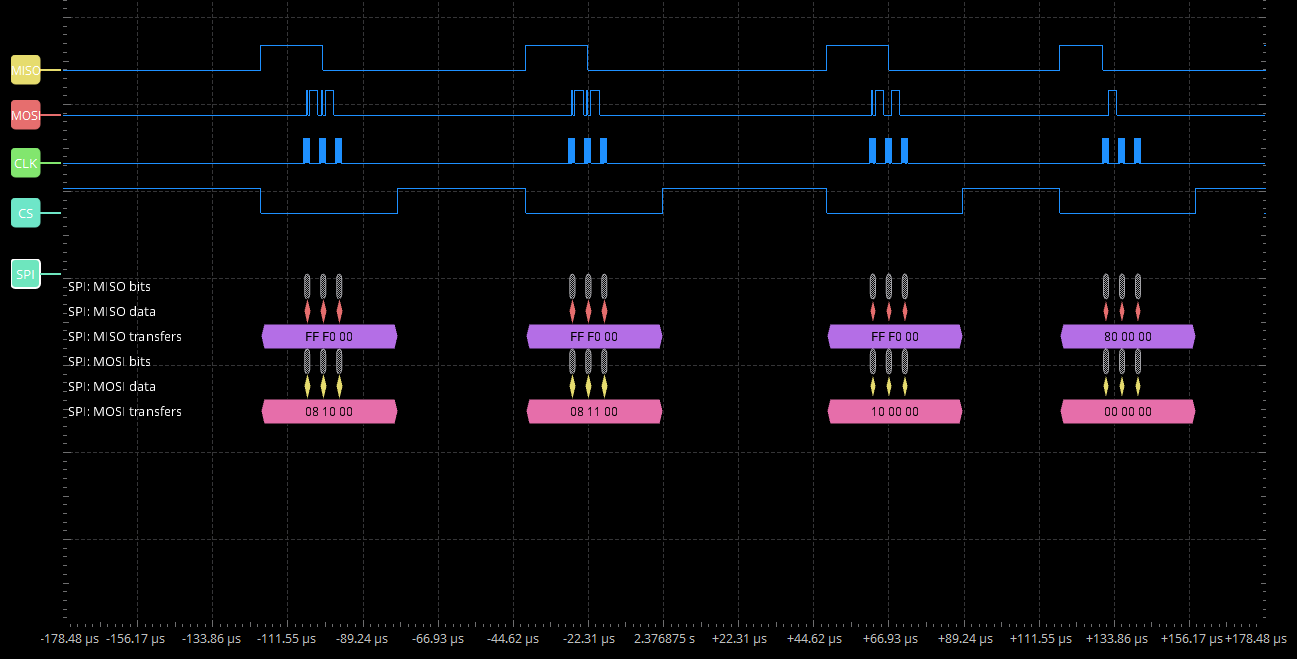

Readback of the init was succesfull. Now the manual conversion setup and channel selection followed by a read to the SYSTEM_STATUS register.

Further reads to the SYSTEM_STATUS register will always return 0x80 (not shown here). Do you have any suggestions what to do?

Greetings