Tool/software:

Hi, I am using the ADS131A04, 16-bit with 4 channel asynchronous interrupt mode,

ADC configurations are:

0x0B A_SYS_CFG 0x78 (VCP off, High res EN, VREF4V, INTVREF)

0x0C D_SYS_CFG 0x3C

0x0D CLK1 0x02 (CLK_DIV=2) 16.384/2=8.192M

0x0E CLK2 0x2F (ICLK_DIV=2, OSR=32) fmod = 8.192M/2 =4.096M, sampling rate 4.096M/32=128ksps

0x11 ADC1 0x00 GAIN1 = 1x

0x12 ADC2 0x00 GAIN2 = 1x

0x13 ADC3 0x00 GAIN3 = 1x

0x14 ADC4 0x00 GAIN4 = 1x

0x0F ADC_ENA 0x0F (all ADCs on)

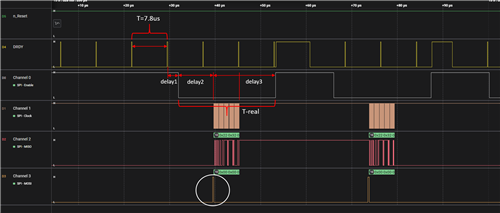

The required sampling rate is 128k samples/sec, but I am not able to get the 128k samples/sec; I am only getting a maximum of 29k samples/sec. Even with 64k samples/sec we are getting only 29K samples.

Here we are using Master device as the Renesas RA6M3 and using a spi clock speed of 15 MHZ.

Please let us know on this what are the other configurations needs to be considered and provide suggestion to achieve this 128ksps.

Thank in Advance