Other Parts Discussed in Thread: LMK04828

Tool/software:

Hello,

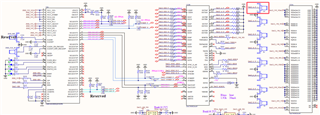

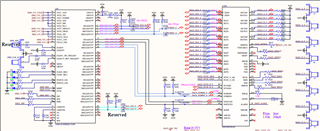

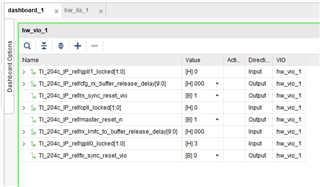

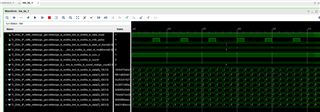

I run a example for DAC38J82 using TI204C-IP.

And I got the register value from 0x64 to 0x6C from DAC38J82. Below is the value.

Reg 0x64 = 0

Reg 0x65 = 0

Reg 0x66 = 0

Reg 0x67 = 0

Reg 0x68 = 0

Reg 0x69 = 0

Reg 0x6A = 0

Reg 0x6B = 0

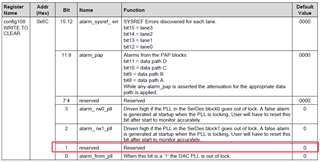

Reg 0x6C = 0x3 ( Bypass DAC PLL)

So I have 2 questions.

Question1: From DataSheet, Reg 0x6C bit1 is reserved and should be 0, but I got 1. Is it normal?

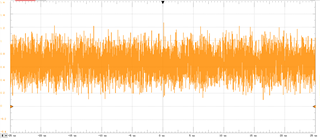

Question2: From the register value, It seems DAC working normal, after pull up TXEN, but I cannot see waveform from output A+. Is it any other possiable?

Thanks

Best regards

Daniel