Tool/software:

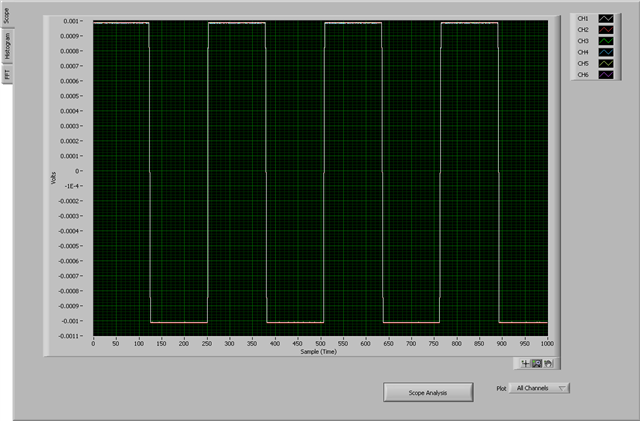

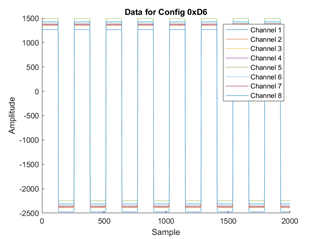

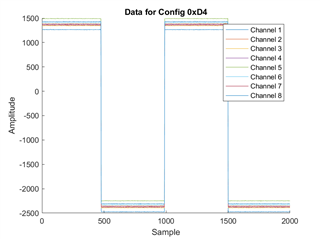

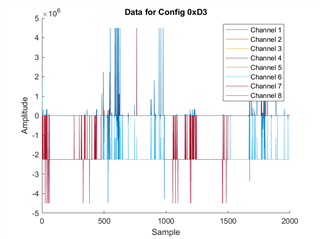

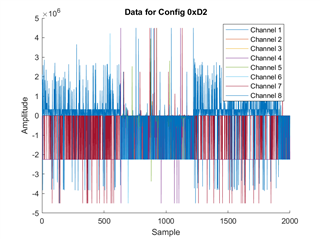

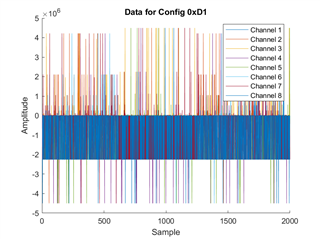

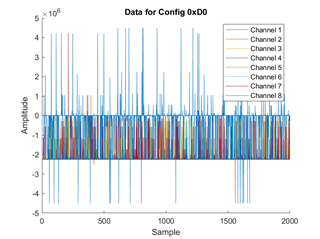

I am in process of programming and controlling ADS1299 using a Microcontroller and for now I am successfully able to read device ID, able to read/write registers and now configured to generate test signal on all channels and plot them on serial port. Below is the screen short of the plot data. I am observing few weried rising/falling edges in test signal. Is it correct ? Currently all the data pins are open and below are my config register settings:

CONFIG1: 96

CONFIG2: D0

CONFIG3: EC

LOFF: 0

CH1SET: 5

CH2SET: 5

CH3SET: 5

CH4SET: 5

CH5SET: 5

CH6SET: 5

CH7SET: 5

CH8SET: 5

BIAS_SENSP: 0

Need opinion if it is correct ? Or any adjustments are required. I want to confirm before proceeding towards biosignals.

Thanks