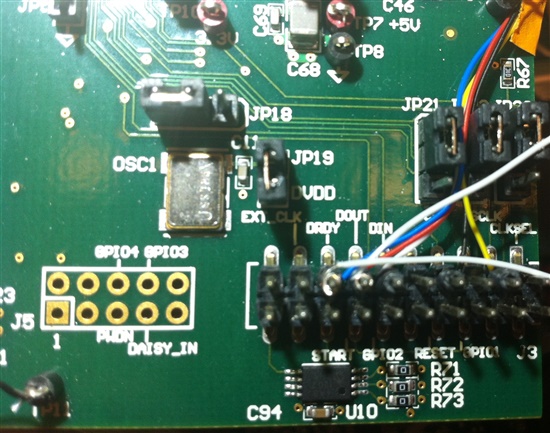

I am trying to read data from DOUT pin in the ADS1299 EEG-FE without the MMB0 board. I have sent a SCLK clock (bottom of the figure) of 8 bits *27 using a 8-bit MCU. The default read data mode of the ADS1299 is RDATAC, right? I can detect correct DRDY_bar and CS_bar signals. But I cannot get signals from the DOUT (above of the figure) if I connect the CH1 with a signal source.

Is it because I am reading the buffer in a byte-by-byte other than 24-bit way? I noticed there is a half T_sclk dalay when a 8 -bit clock is generated. Does it matter?

Or I should configure some registers of ADS1299 first so that it can send data?

Thank you for some advices.