We are using the ADS1256 to measure several NTC voltage and currents (voltage on Rsense).

The ADC is connected to a Zynq FPGA where we have an SPI module interfacing with the ARM core.

We observed a strange behavior when we restart the measurement: within in the loop the stability is quite good, around 0.01 C degrees , but in the next loop we randomly see an offset of 0.2C degree.

We did a measurement with a FIX resistor (we replaced the NTC) to check the stability. The temperature calculated from this resistor is around 25C. But we observed certain 'offset jumps' between measurement loops. See screenshot.

We were monitoring the SPI wires to see if it is a SW (FPGA / C-code) issue in data-postprocessing or these 'jumps' are already coming from the ADC.

Well, they are coming from the ADC.

Some measured hex values (measured on the AN01 input):

- Loop 1 .

- 0x6F 54 D1

- 0x6F 54 C2

- Loop 2 .

- 0x6F D1 95

- 0x6F D2 0B

- Loop 3.

- 0x6F 8F 2F

- 0x6F 8E 30

The differences within the loop is quite small, but between loops you see that the middle byte is changing.

We assume that the cause is somewhere around the configuration of the ADC that we use.

Here is the pseudo code of what we do:

Init() //run at every loop start

{

Cmd RESET

Wait_DRDY_HIGH

Cmd RESET

Wait_DRDY_HIGH

Cmd WREG DRATE, 0, 0xB0

Cmd STANDBY

Cmd WAKEUP

Wait_DRDY_HIGH

Cmd RREG DRATE

Cmd STANDBY

Cmd WREG GPIO, 0, 0

Wait_DRDY_HIGH

Cmd WREG ADCON, 0, 1

Cmd WREG STATUS, 0, 2

Wait_DRDY_HIGH

Cmd SELFCAL

}

//this runs in an FPGA VHDL FSM…

// same as the Fig19 in ADS1256 pdf (ver. Sept 2013)

Fpga_Meas()

{

Cmd WREG to change MUX

Cmd SYNC

Cmd WAKEUP

Cmd RDATA

Wait_t6;

RD data

}

Main()

{

Init()

For ( 10)

{

Cmd WAKEUP

For (100)

{

Fpga_Meas()

}

Cmd STANDBY

Wait_2sec

}

}

Note: this main function now mimics a more complex SW where we originally saw this issue.

Do you have any hints where to look for the cause?

Thanks,

Andras

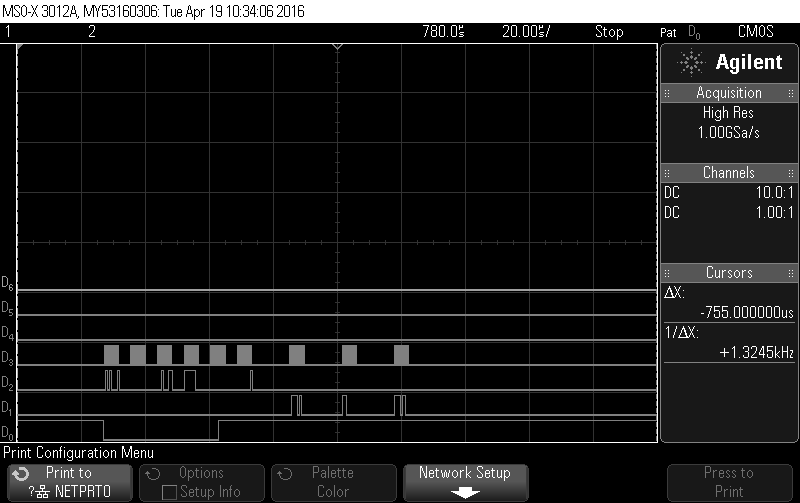

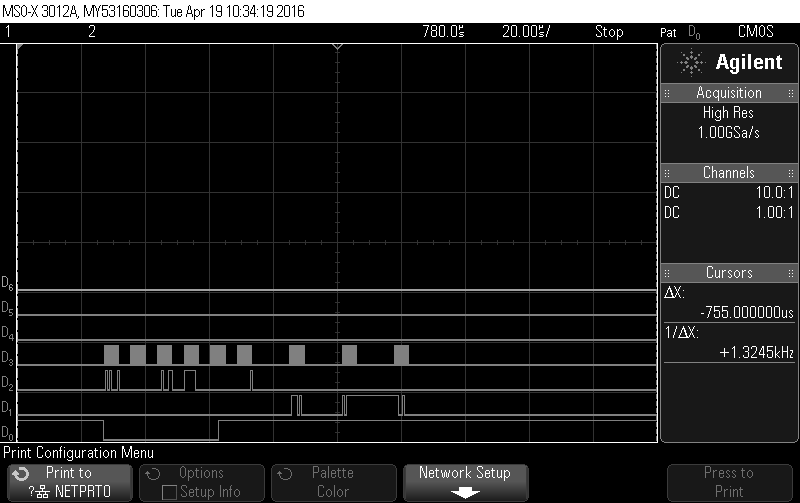

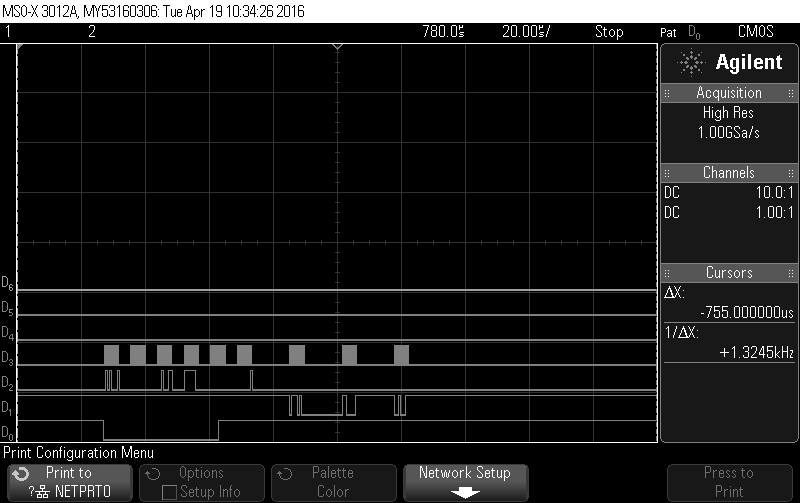

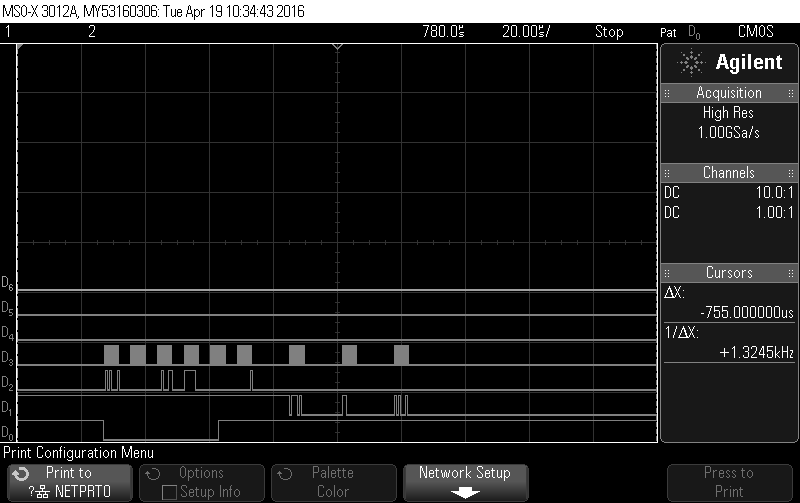

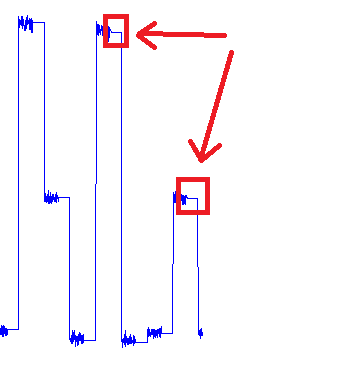

update: I have created some screenshots of the scope to show how the middle byte of the data is behaving.

D3: SCLK

D2: DIN

D1: DOUT

D0: DRDY

It also shows that the timing of DRDY-to-RDATA-retrival is always the same.

#1

#2

#3

#4