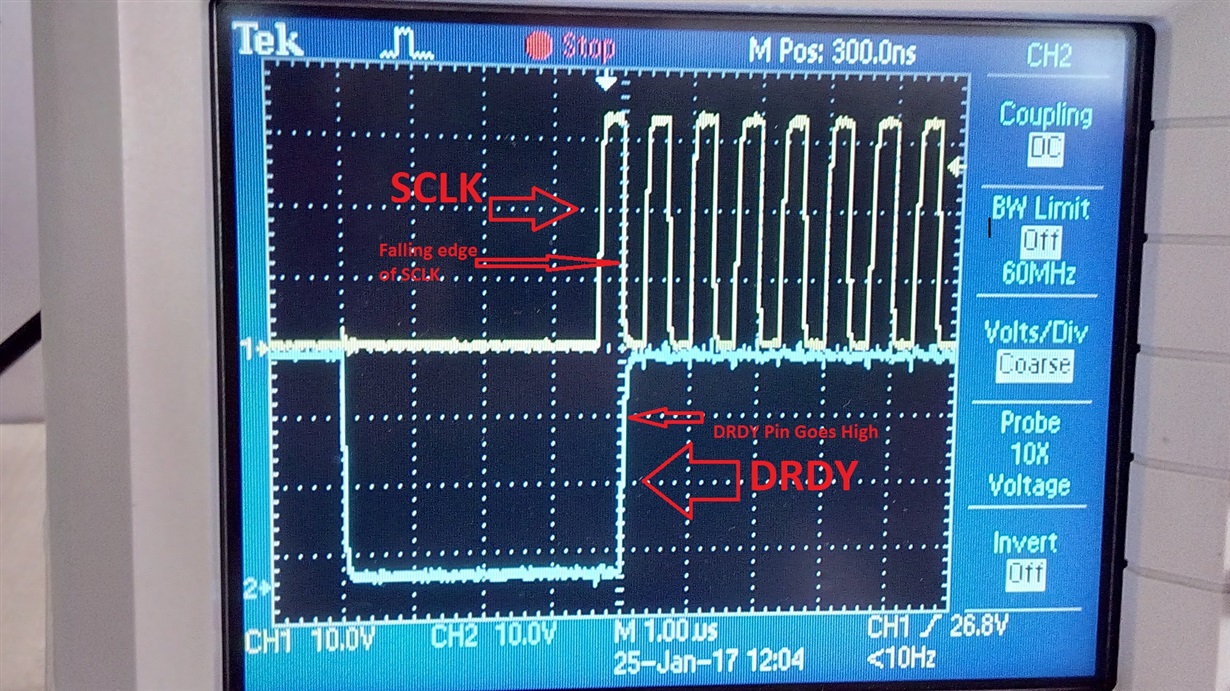

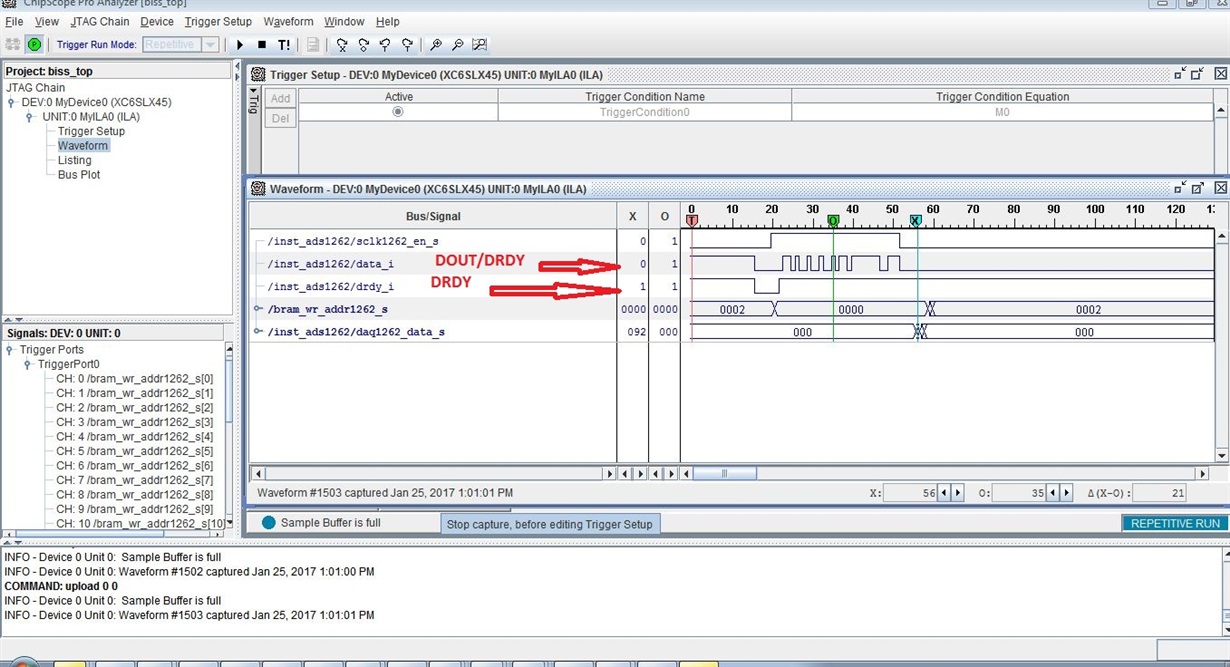

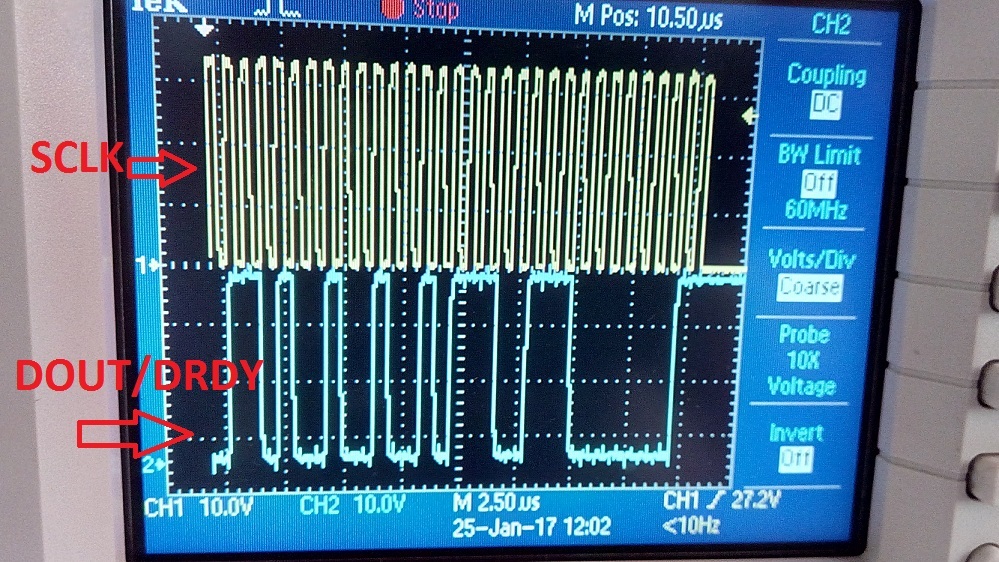

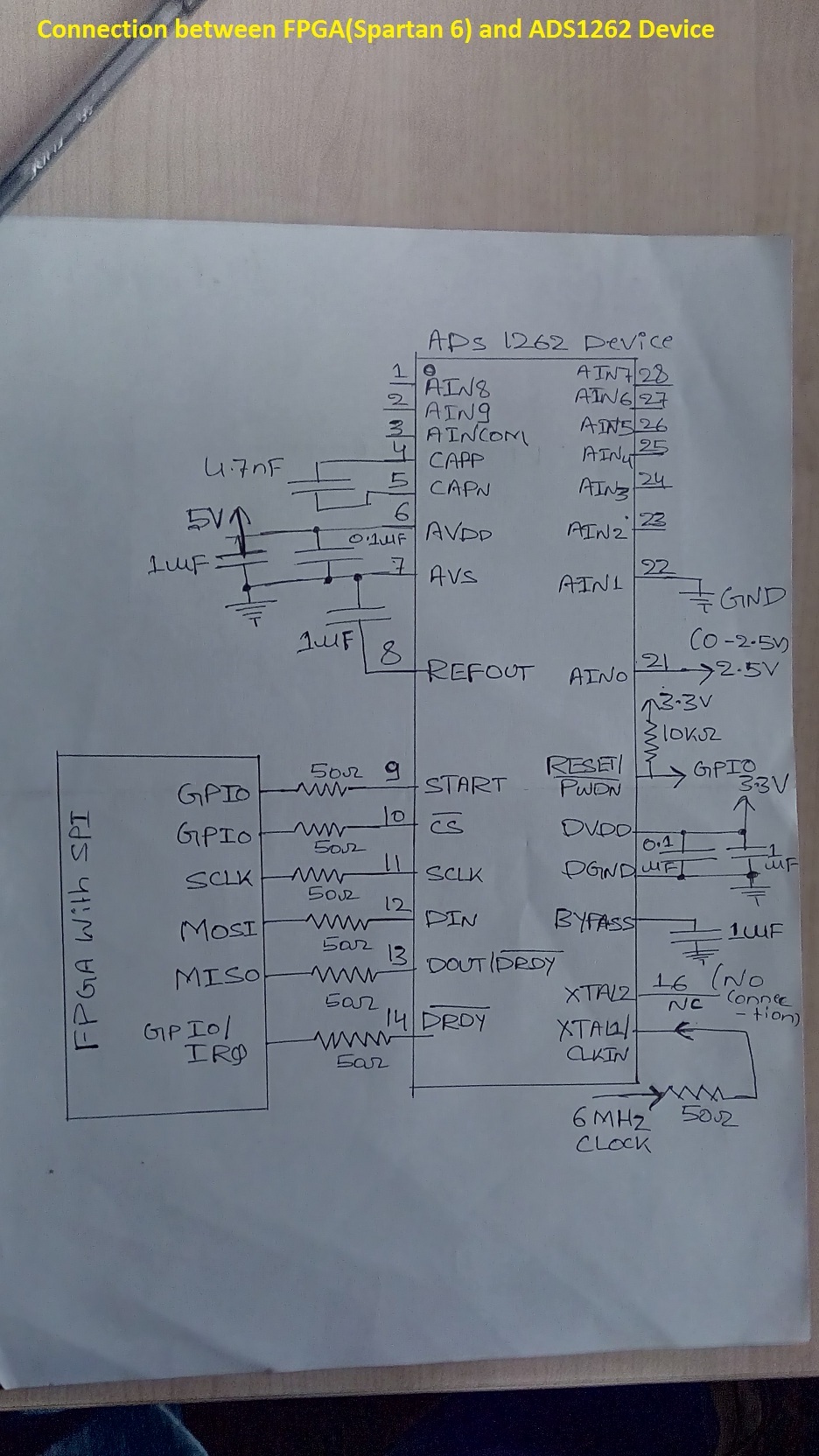

I have been using ads 1262 connecting with FPGA .I have written code in VHDL, data conversation can be seen by checking pin DOUT/DRDY, but unable to capturing serial data coming DOUT/DRDY pin.I have configured all analog and digital voltages as per data sheet. I am using shift register method to update data(SIPO Register).

The below will code i written in VHDL

when start_adc_conv_st =>

if(start_i = '1') then

start <= high;

start_adc_counter <= start_adc_counter + 1;

if(start_adc_counter = 4) then

start <= low;

adc_1262 <= start_adc_conv_st1;

end if;

else

start <= low;

adc_1262 <= start_adc_conv_st;

end if;

when start_adc_conv_st1 =>

if(start_adc_counter = 8 ) then

start <= high;

start_adc_counter <= 0;

adc_1262 <= drdy_detect1_st;

else

start_adc_counter <= start_adc_counter + 1;

start <= low;

adc_1262 <= start_adc_conv_st1;

end if;

when drdy_detect1_st =>

if(drdy_i = '1') then

adc_1262 <= drdy_detect2_st;

else

adc_1262 <= drdy_detect1_st;

end if;

when drdy_detect2_st =>

if(drdy_i = '0') then

sclk_enable_s <= high;

bram_wr_cntr <= 06;

-- drdy_wait_cntr <= 0;

-- test_data <= (others => '0');

bram_wr_addr_s <= (others => '0');

adc_1262 <= data_collect_st;

else

adc_1262 <= drdy_detect2_st;

end if;

when data_collect_st =>

if(ch1_cntr = low_cnt) then

sclk_enable_s <= low;

bram_wr_en_s <= high;

adc_1262 <= bram_write_data_st;

else

if(rd_en1_i = '1') then

received_data <= received_data(30 downto 0) & data_i;

ch1_cntr <= ch1_cntr - 1;

if(ch1_cntr = 5) then

sclk_enable_s <= low;

end if;

end if;

adc_1262 <= data_collect_st;

end if;

when bram_write_data_st =>

if(bram_wr_cntr = low_cnt) then

bram_wr_en_s <= low;

ch1_cntr <= 32;

cntr <= 0;

received_data <= (others => '0');

adc_1262 <= drdy_detect1_st;

else

bram_wr_addr_s <= bram_wr_addr_s + 1;

bram_wr_cntr <= bram_wr_cntr - 1;

adc_1262 <= bram_write_data_st;

end if;

when others =>

null;

end case;

end if;

end process;

Thank you inadvance