HI,

- C48 - Changed to 1uF.

- C31, C42 - Changed to 1500pF

- J72, J73, J62, J51, J50 - Shunt Jumpers ON

- J53, J60, J34, J32 - Shunt Jumpers OFF

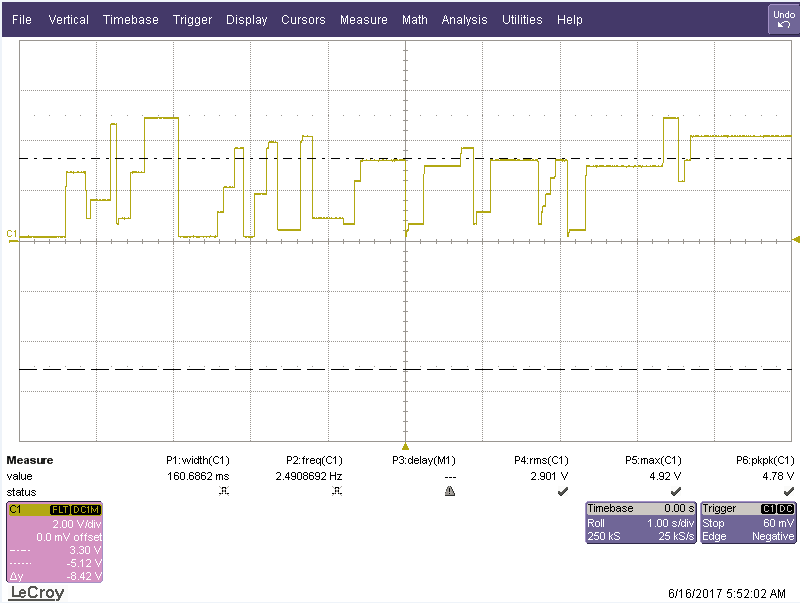

- Under this condition the O/P at J73 in this particular board is 5.010V. We see the following on J53 & J60 on the chipside:

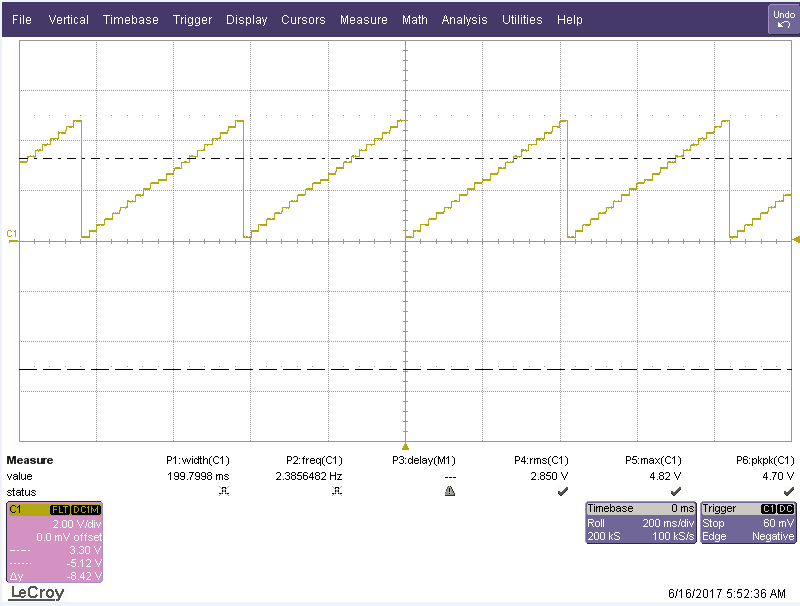

- However if we remove the jumper J73 and feed a voltage between 4.950 - 5.005V on the 5V side, we see the following:

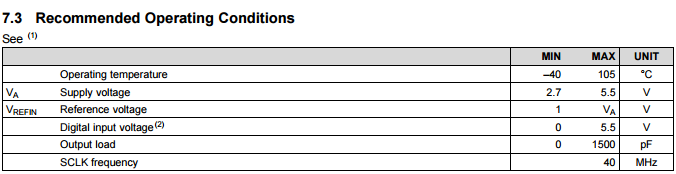

- DAC I/P voltage range according to datasheet:

We would like to know what is going wrong here.