Other Parts Discussed in Thread: TLV5606

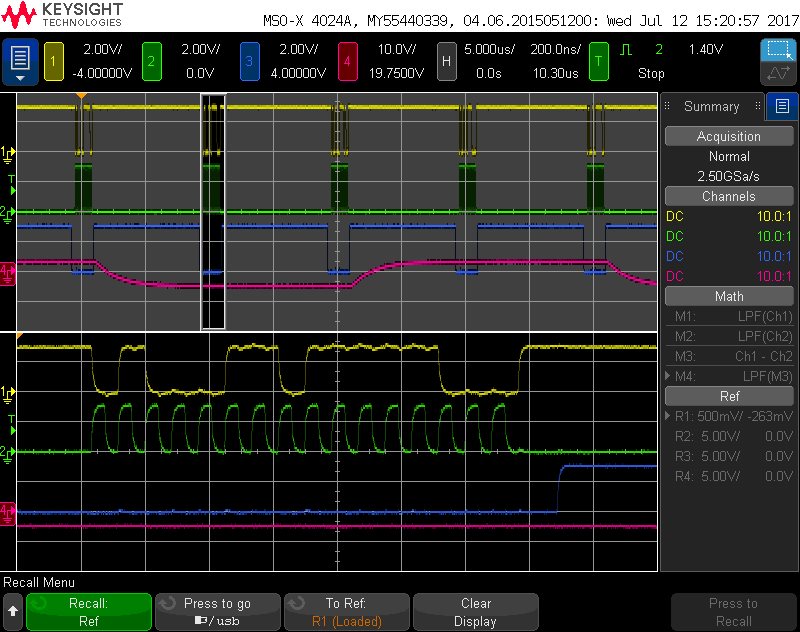

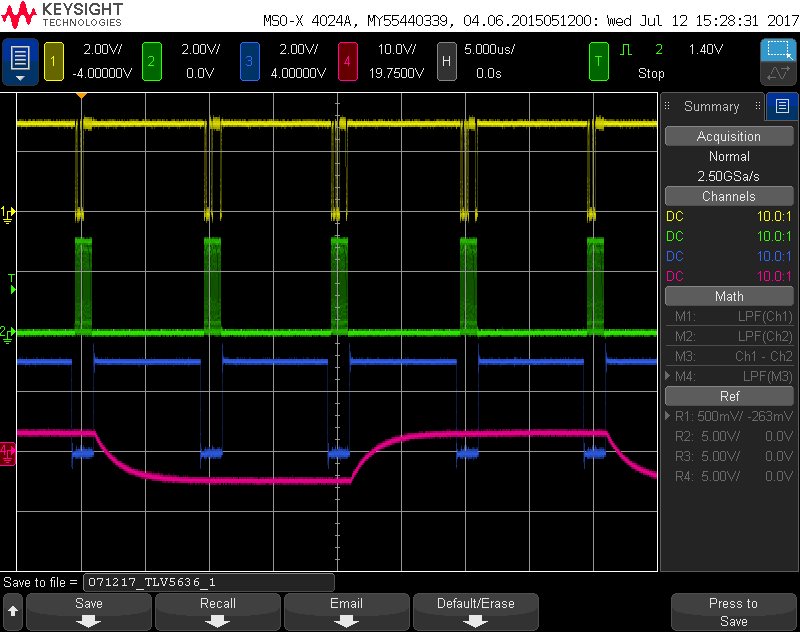

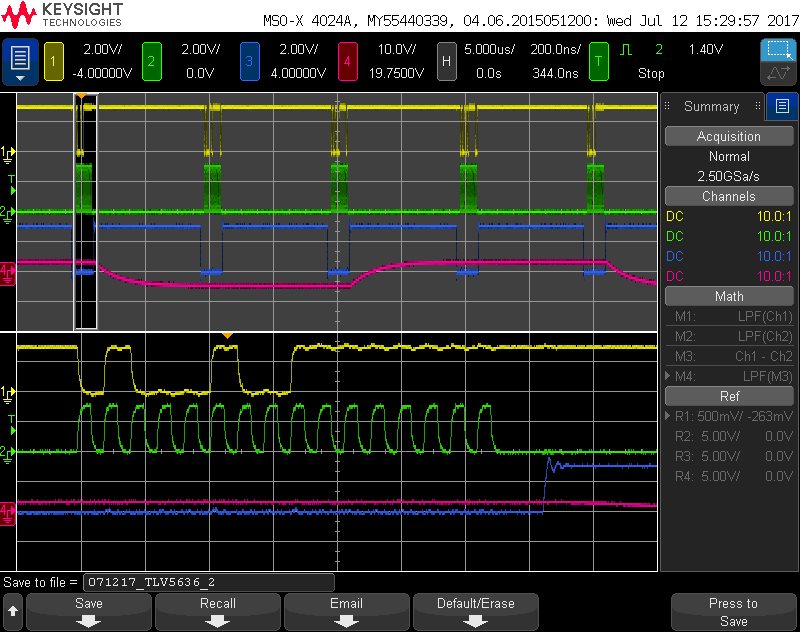

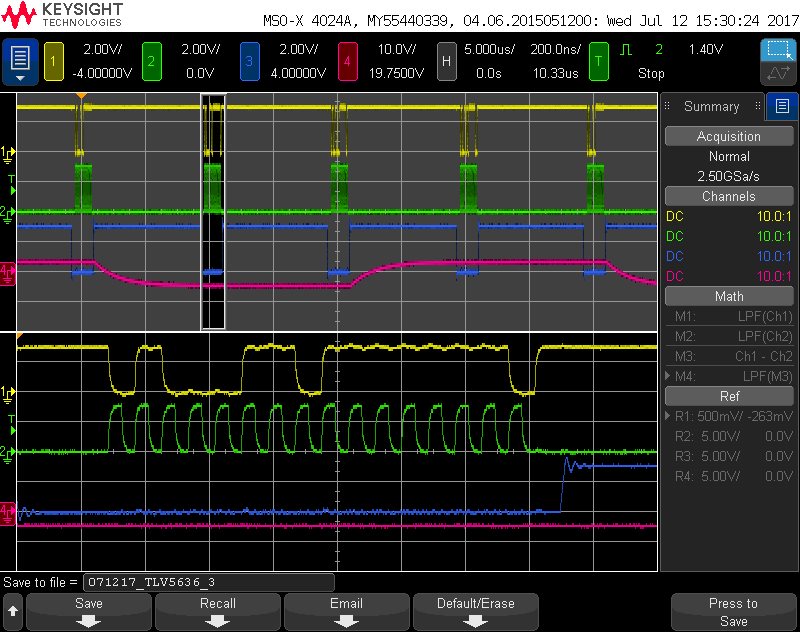

I am using the TLV5636 12-bit DAC. I have noticed by single stepping through the debugger that the first DAC register write immediately following a Reference Select control register write is IGNORED. A second DAC write (immediately) is accepted and the output follows the DAC write value. Any thoughts? Any unwritten/unpublished errata concerning this part and the proper write procedures?

_TLV56xx_Write.ucResolution = RES_UNKNOWN;

_TLV56xx_Write.ucReferenceBitMap = REF2048;

_TLV56xx_Write.wDataValue = 0;

_TLV56xx_Write.bPowerDown = RSC_FALSE;

//============================================================

// Step 1

//============================================================

// turn ON transmitter

Tx_Enable_On();

Pause(10);

// 12 bit DACs must also have their reference source specified

// Start with REF2048

_TLV56xx_Write.ucWriteMode = CONTROL_WRITE;

_TLV56xx_Write.ucReferenceBitMap = REF2048;

TLV56xx_SPI_Write(&_TLV56xx_Write);

// put something near zero load current into the DAC

_TLV56xx_Write.ucResolution = RES_12BIT;

_TLV56xx_Write.ucWriteMode = DAC_WRITE;

// should be close to mid point for either 10 or 12 Bit using TLV56xx_SPI_Write

_TLV56xx_Write.wDataValue = 0x07FC;

// for reasons that I do not fully understand, the first DAC_WRITE after a CONTROL_WRITE is ignored!!

TLV56xx_SPI_Write(&_TLV56xx_Write);

// repeat

TLV56xx_SPI_Write(&_TLV56xx_Write);

void TLV56xx_SPI_Write(TLV56xx_WRITE_ASSIST *pTLV56xx_Write_Assist)

{

volatile WORD wData;

wData = (0x0FFF & (pTLV56xx_Write_Assist->wDataValue));

if (pTLV56xx_Write_Assist->bPowerDown)

{

// DAC register write

pTLV56xx_Write_Assist->ucHighByte = POWER_DOWN_BIT;

pTLV56xx_Write_Assist->ucLowByte = 0x00;

}

else if (pTLV56xx_Write_Assist->ucWriteMode == CONTROL_WRITE)

{

// only applicable to TLV56xx devices with a reference control register

// Control register write, POWER_DOWN_BIT is forced to RSC_FALSE

pTLV56xx_Write_Assist->ucHighByte = REG_SEL_BIT_MAP;

pTLV56xx_Write_Assist->ucLowByte = pTLV56xx_Write_Assist->ucReferenceBitMap;

}

else if (pTLV56xx_Write_Assist->ucWriteMode == DAC_WRITE)

{

// DAC register write

if (pTLV56xx_Write_Assist->ucResolution == RES_10BIT)

{

// shift 10 bit data value to correct bit positions

wData = wData << 2;

wData &= 0x0FFC;

}

pTLV56xx_Write_Assist->ucHighByte = (UCHAR) (wData >> 8);

pTLV56xx_Write_Assist->ucLowByte = (UCHAR) (wData & 0x00FF);

}

pTLV56xx_Write_Assist->ucHighByte |= FAST_BIT;

B2_SPI_ASSERT_CS();

B2_SPI_ASSERT_FS();

B2_SPI_DataPut(pTLV56xx_Write_Assist->ucHighByte);

B2_SPI_WaitOnTransmit();

B2_SPI_DataPut(pTLV56xx_Write_Assist->ucLowByte);

B2_SPI_WaitOnTransmit();

B2_SPI_WaitOnBusy();

B2_SPI_DEASSERT_FS();

B2_SPI_DEASSERT_CS();

}