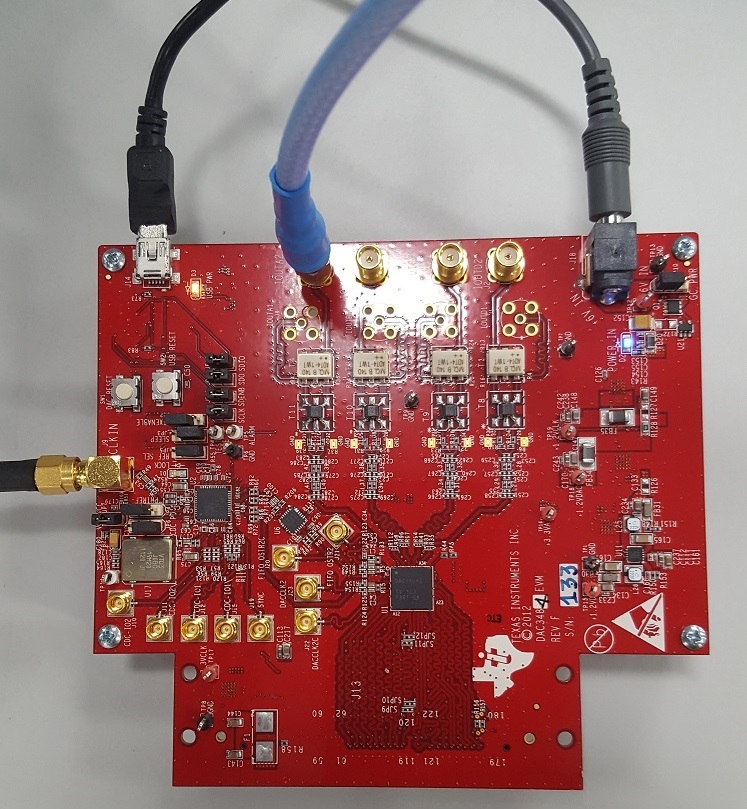

Other Parts Discussed in Thread: CDCE62005, TRF3722, DAC3482

Hi

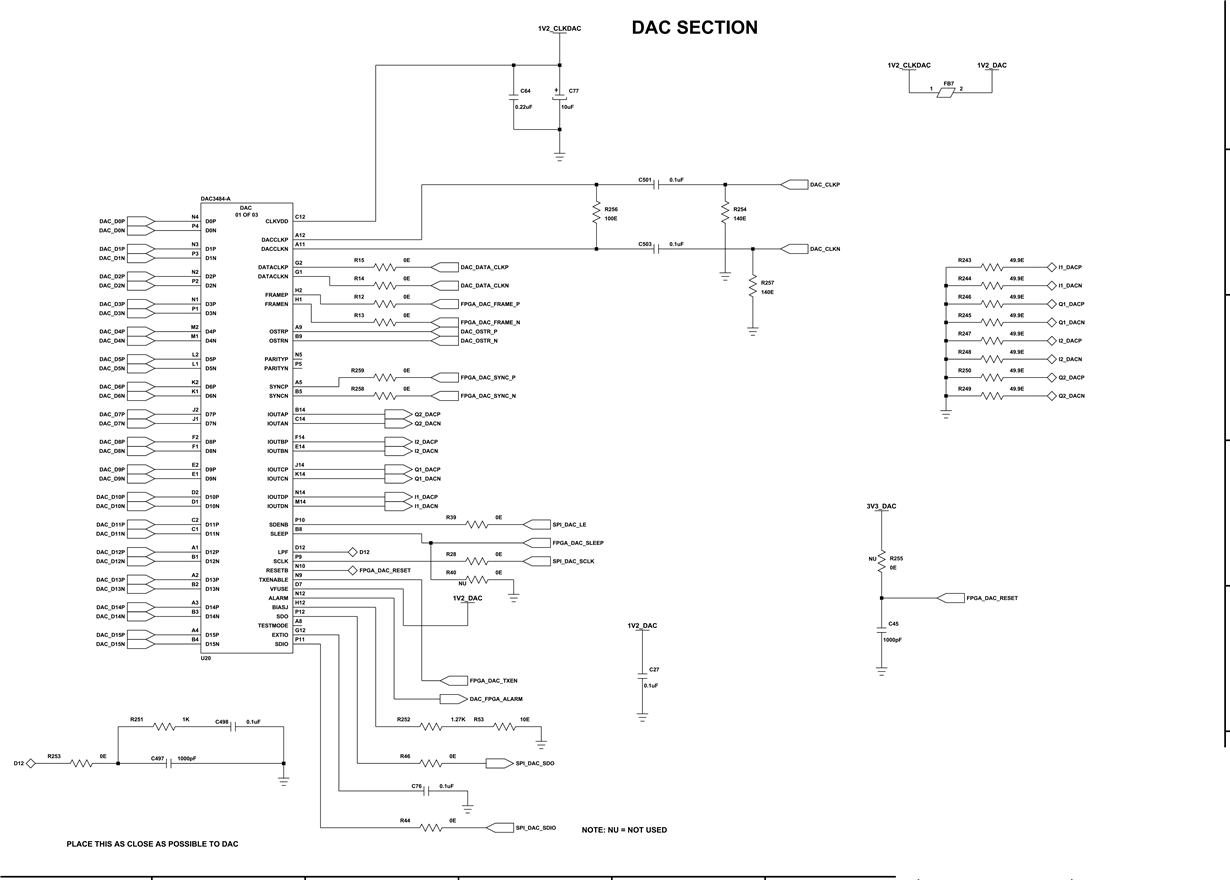

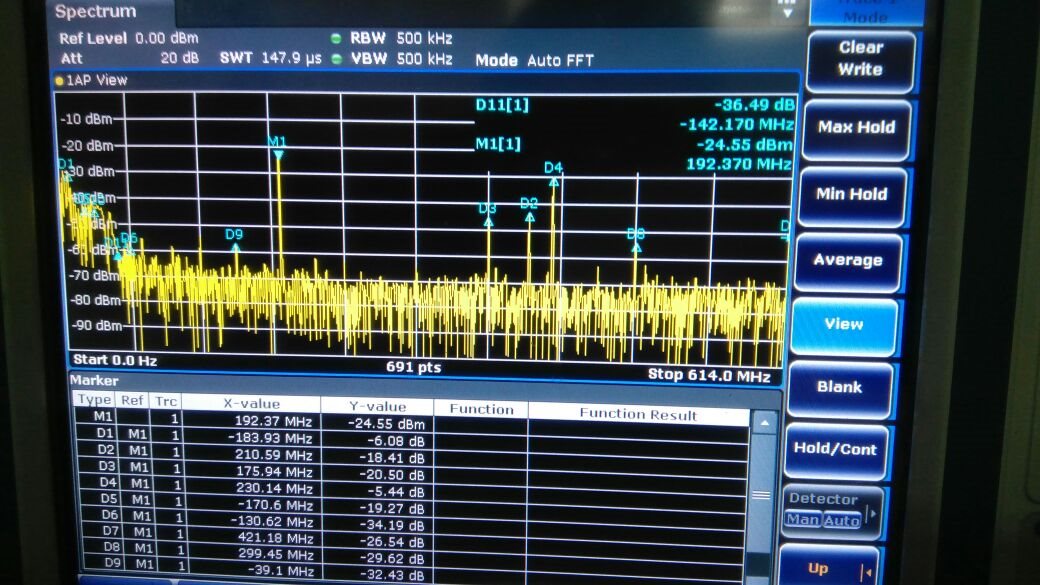

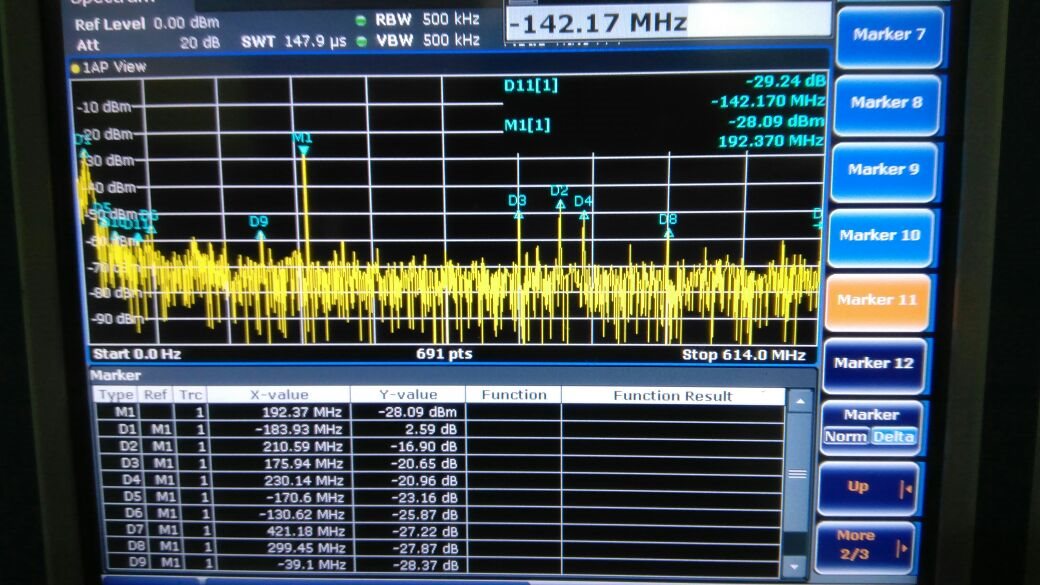

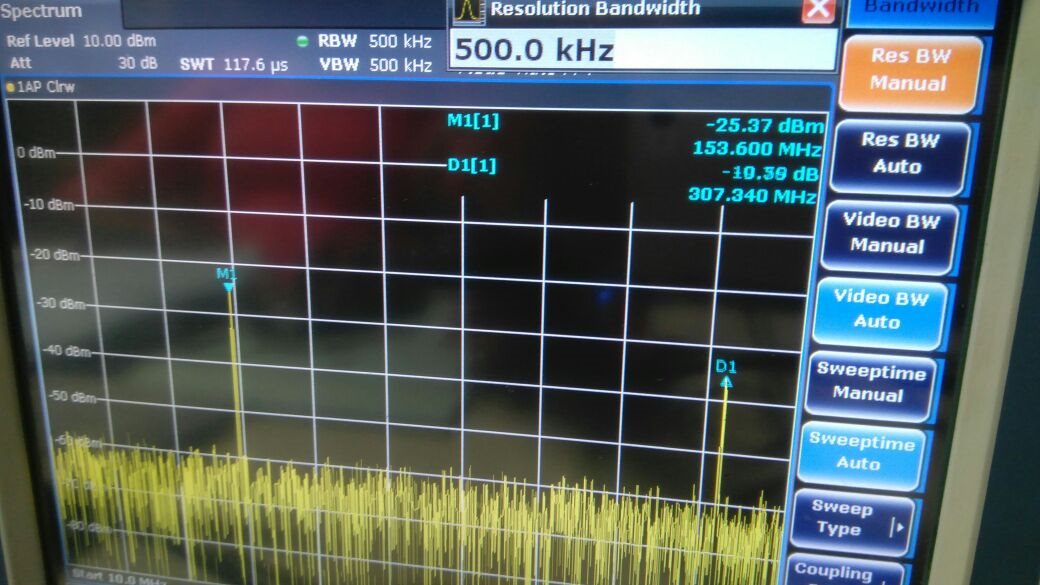

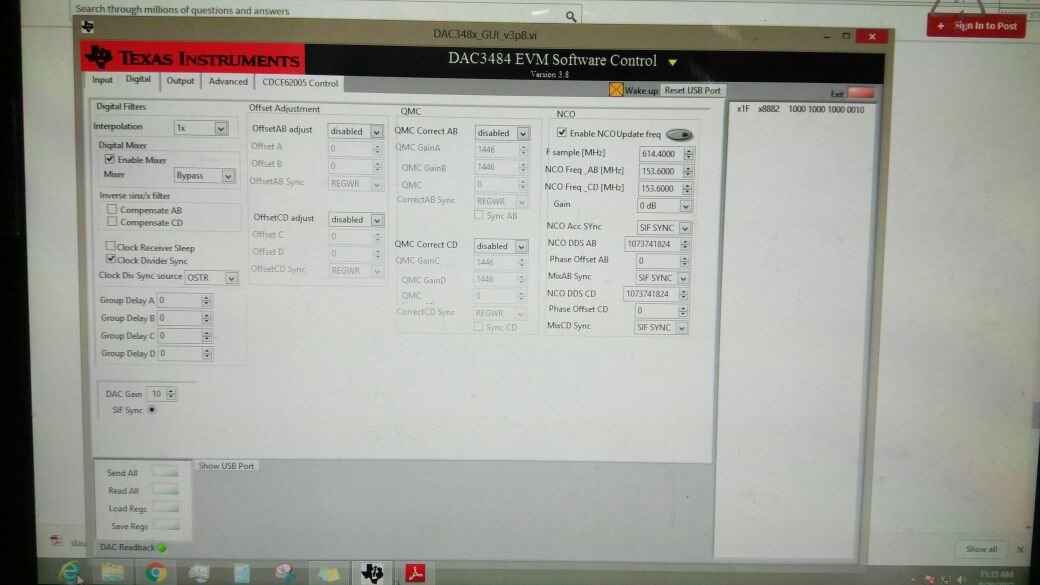

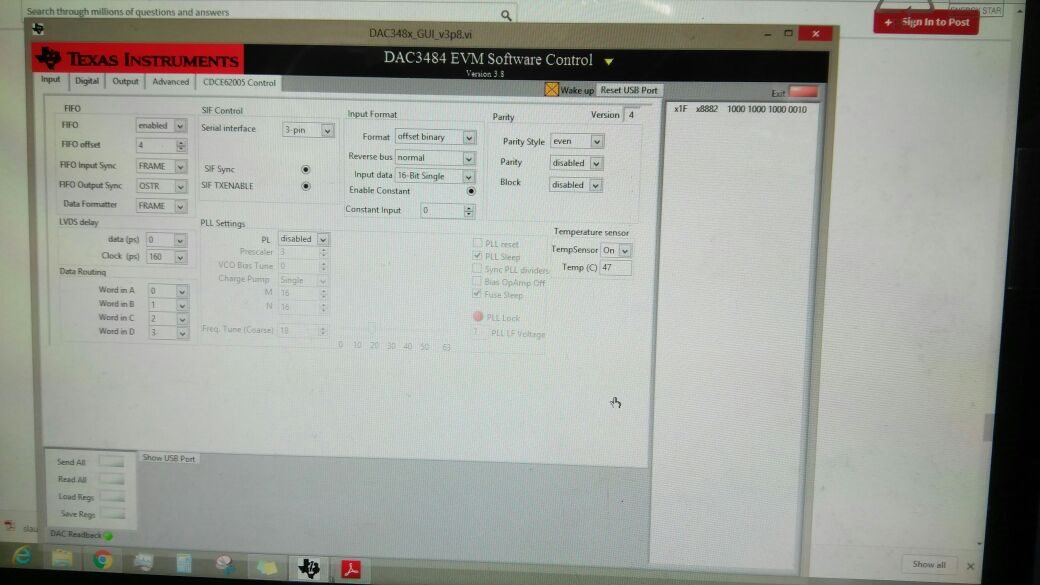

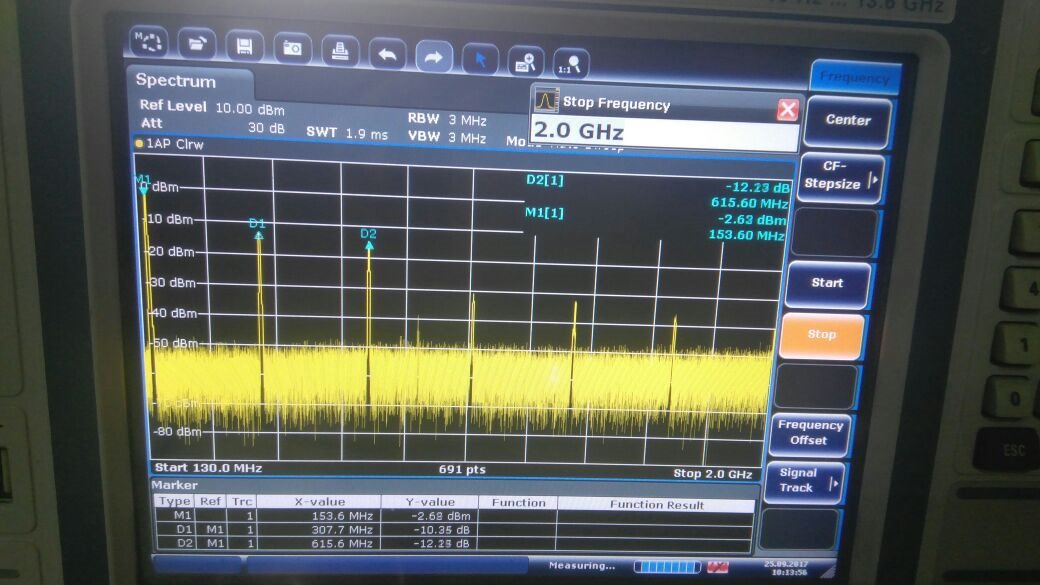

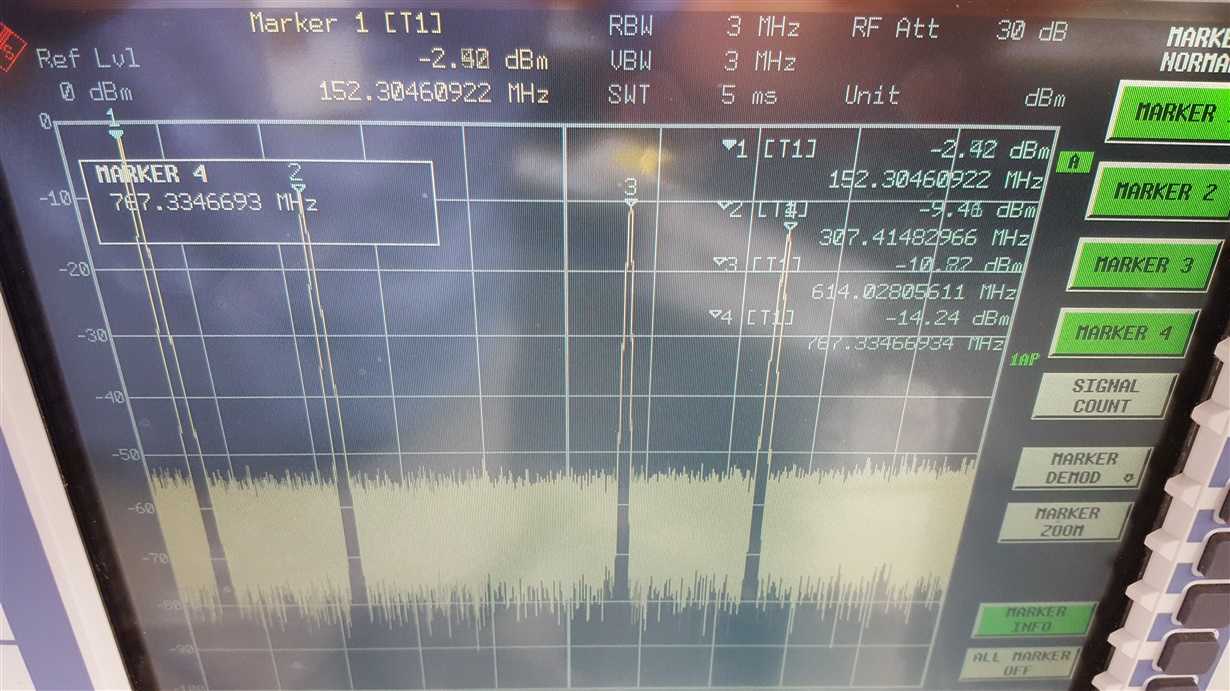

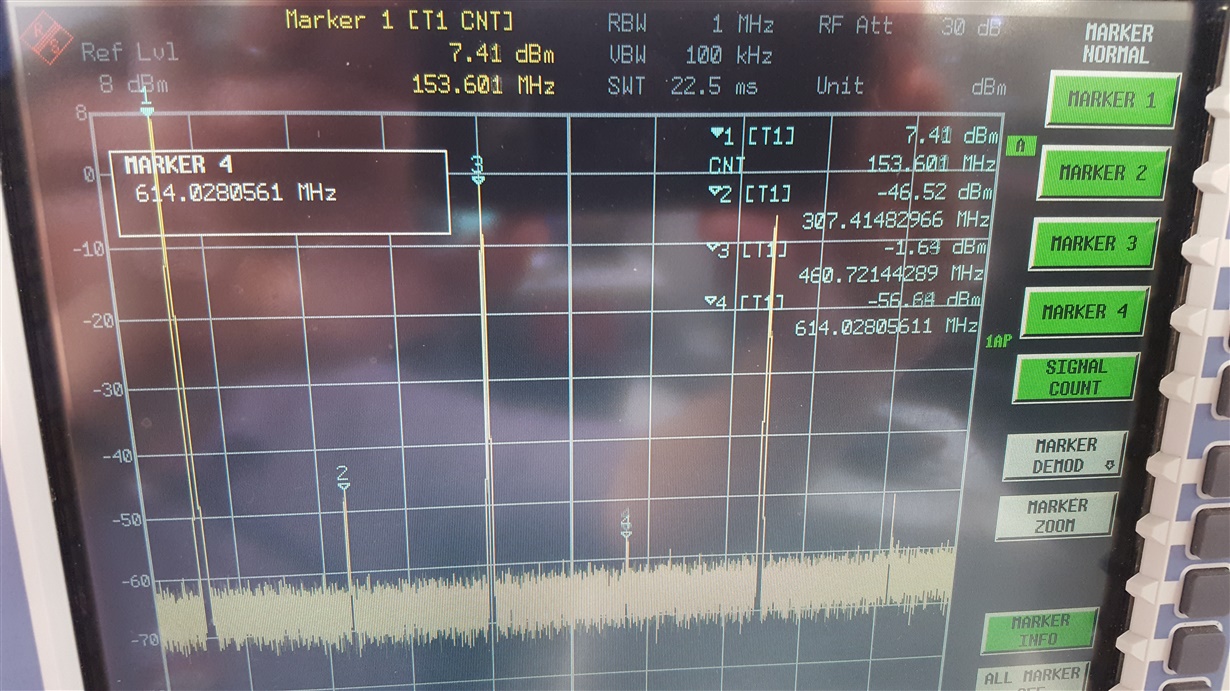

DAC CLK= 614.4 MHz

DATA CLK=307.2MHz

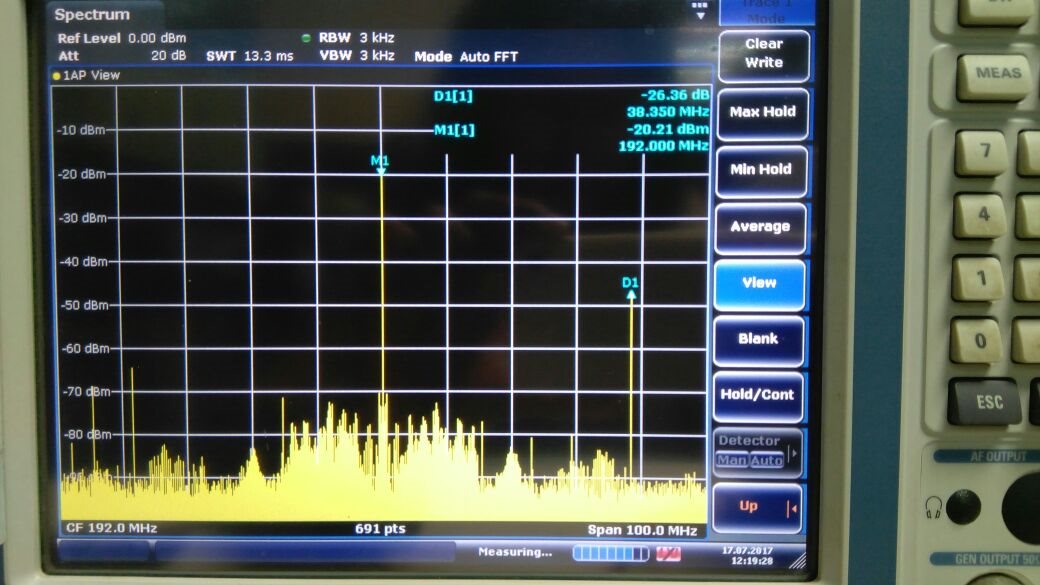

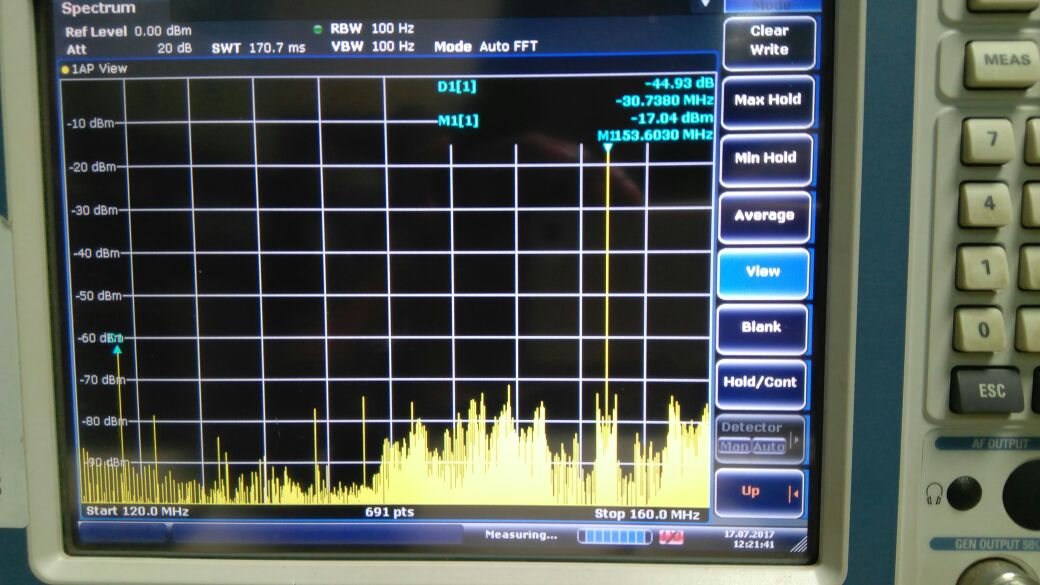

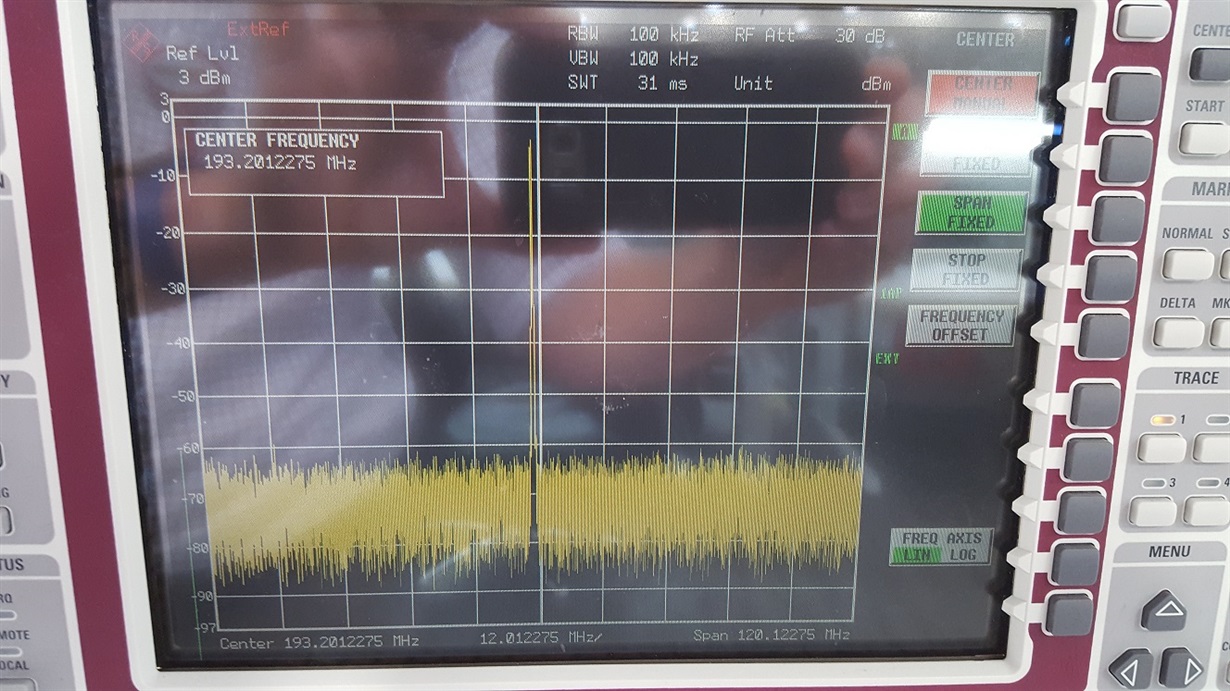

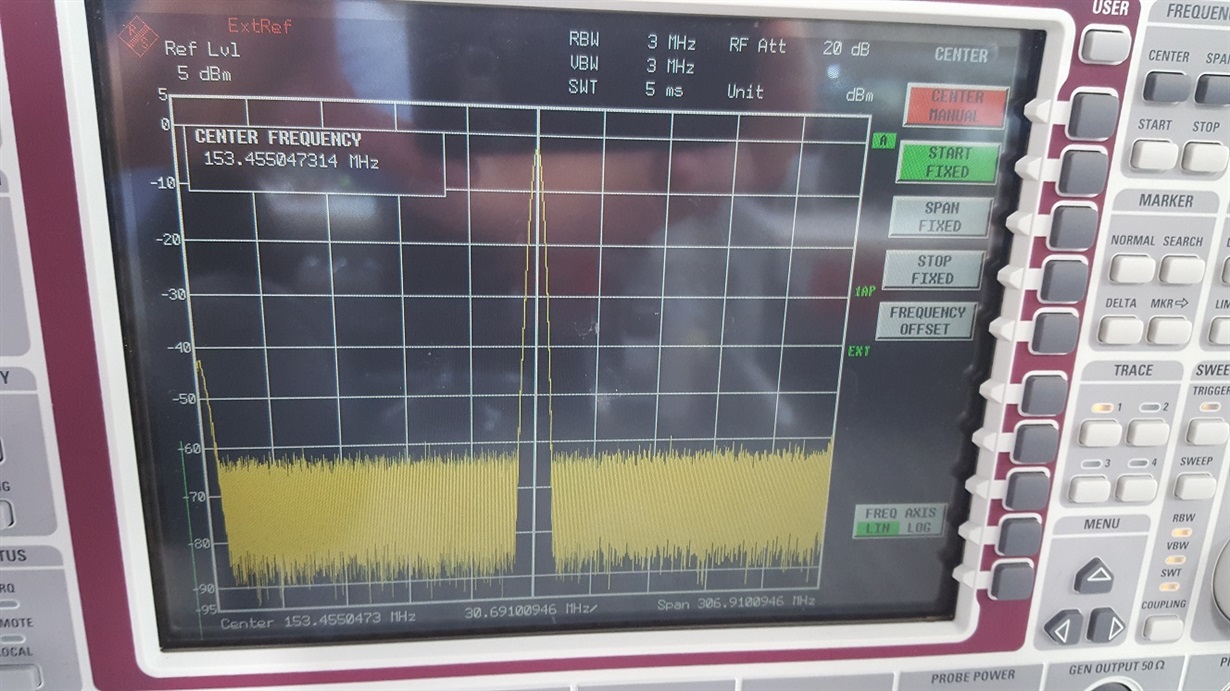

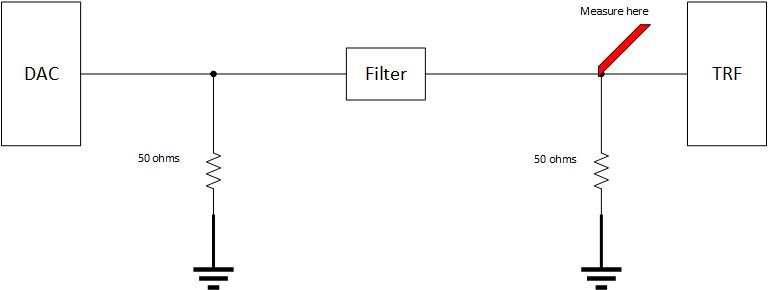

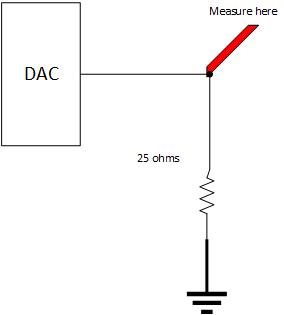

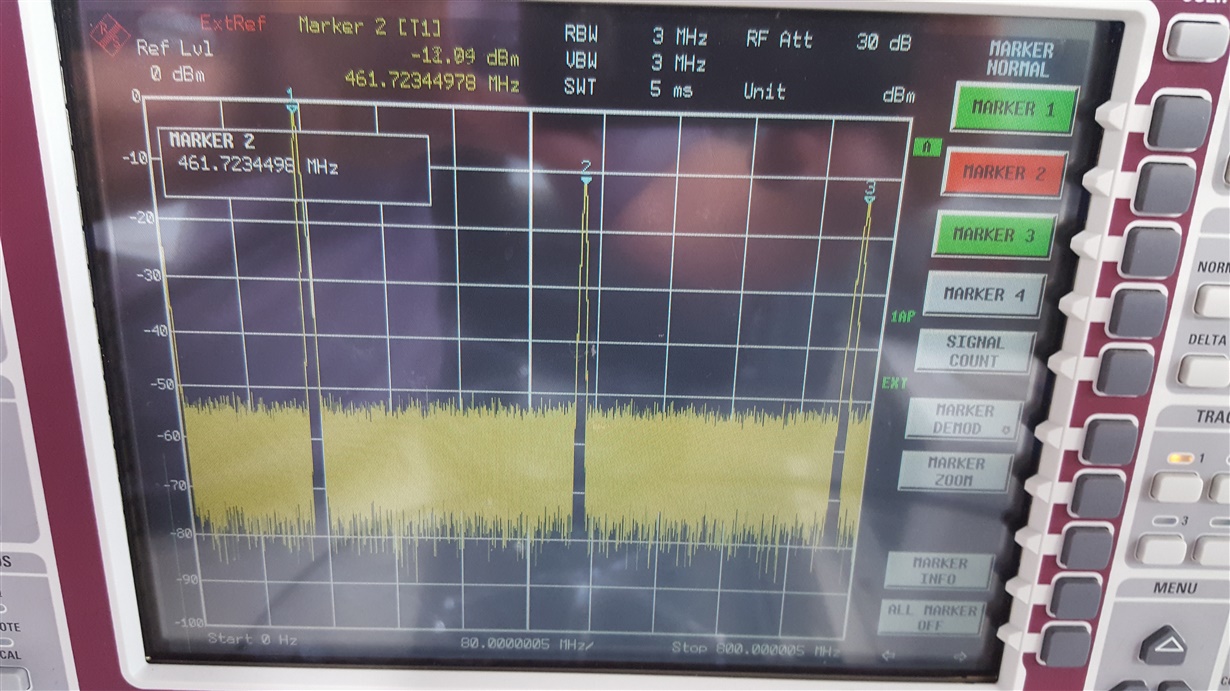

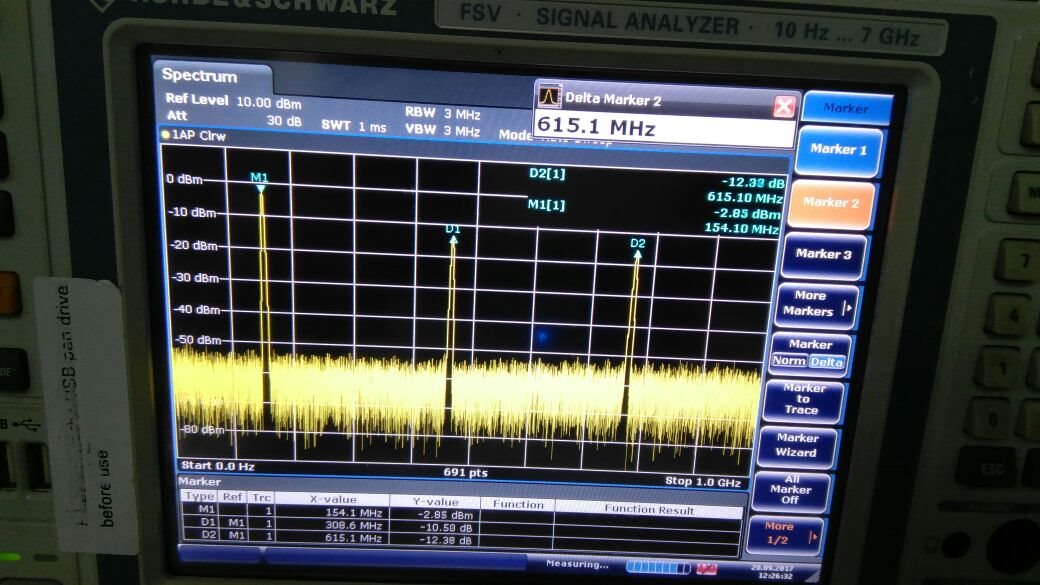

We are using DAC at self test mode and kept coarse gain at 1111, with Rbias=1.28k as recommended. Programming the code at 7FFF. (We are using sif_sync) Still the output is not as per datasheet. Moreover, we are getting one prominent spurious at the output which changes with output frequency. I am attaching images of DAC output for one channel at 192MHz output and othe rat 153.6MHz output. Since the spurious changes with frequency as seen in the pictures, when we sweep the output using NCO, we can see our main output sweeping with the spurious sweeping from opposite direction (as it changes with output frequency).

Please suggest a solution to this.

Please note that the large number of spurious other than the prominent ones may be because I have probed the DAC output and these might be pick ups from it.