Other Parts Discussed in Thread: ADCPRO, ADS1263

Hi TI Team,

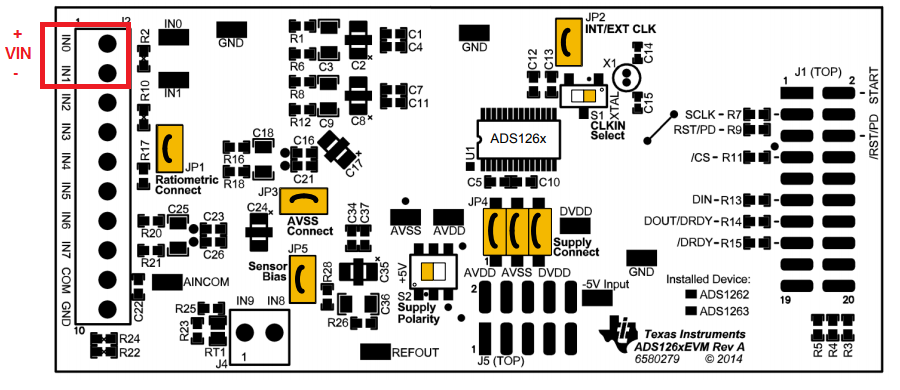

We have experienced a certain shift after collecting data for a long time. Please see the pictures below. Would you please help us solve this problem with correct ADCPro settings? Thank you very much.