Part Number: DAC8775

Other Parts Discussed in Thread: DAC8760, DAC8551

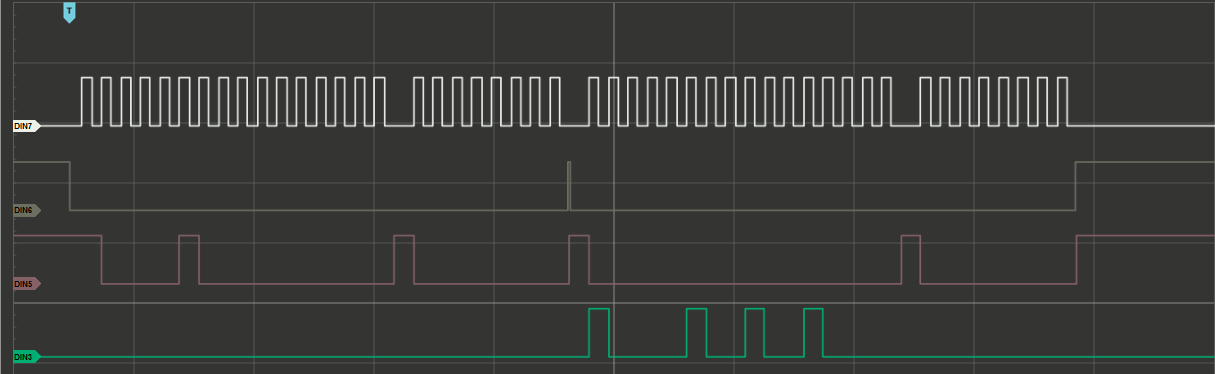

Are there any special preconditions before writing to the DAC8775 DAC data register (address 0x5) other than selecting it? Regardless of the value I write, it reads back as zero. Any other registers read back the same as written (with the exception of, e.g., the reset register's RST bit).

Here is some pseudo code and the values read back:

call anlg_out1_reset

- toggle DAC \reset pin low for 62us, then high

- call spi_write_3bytes(0x01, 0x00, 0x01) ; // software reset

call anlg_out1_configure ;

call anlg_out1_readback_reset_config_register ; // 0x82 1e 02

call anlg_out1_readback_status_register ; // 0x8b 17 80

call anlg_out1_bb_select_a

call anlg_out1_readback_bb_select_register ; // 0x86 00 01

call anlg_out1_readback_bb_config_register ; // 0x87 02 1f

call anlg_out1_dac_select_a

call anlg_out1_readback_dac_select_register ; // 0x83 00 20

call anlg_out1_readback_dac_config_register ; // 0x84 90 00

call anlg_out1_readback_cal_enable_register ; // 0x88 00 00

call anlg_out1_readback_gain_register ; // 0x89 80 00

call anlg_out1_readback_zero_register ; // 0x9a 00 00

call anlg_out1_readback_dac_config_register ; // 0x84 90 00

call anlg_out1_dac_data(0x4001) ; // write 0x4001 to DAC A

call anlg_out1_readback_data_register ; // 0x85 00 00

call anlg_out1_dac_data(0xc002); // write 0xc002 to DAC A

call anlg_out1_readback_data_register ; // 0x85 00 00

Any suggestions?

BTW, I also tried configuring the DAC output, then enabling it in two steps, per this post

https://e2e.ti.com/support/data_converters/precision_data_converters/f/73/p/633490/2338051?tisearch=e2e-sitesearch

without any change in the result.

Thanks.

Joe