Other Parts Discussed in Thread: DDC1128

Dear Specialists,

My customer is testing DDC11C128EVM and has inqries.

I would be grateful if you could advise.

---

We are proceeding with verification on the evaluation board of DDC 1128, but I do not know the details of the data from the software attached to that board.

Now it is a situation that I am in trouble judging whether evaluation results are appropriate.

I would like to confirm about this.

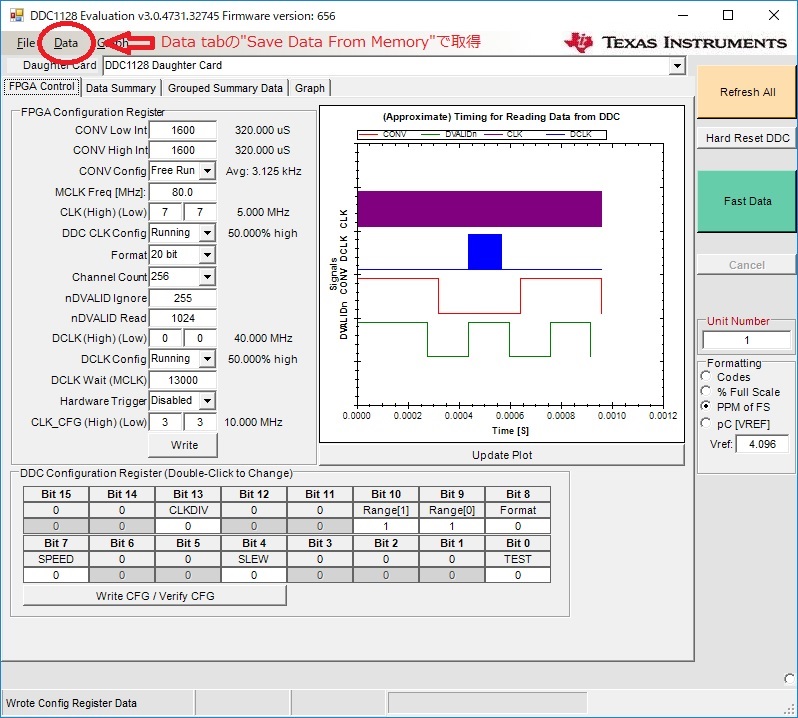

In the state of setting (DDC1128 EVM_Setting.jpg) as shown in the attached figure, data is acquired by Save data memory.

At this time, when acquiring data when setting the value of Bit 8 of the configuration register of the DDC 1128 to 0,

Is it correct to set the FPGA to 16 bits too?

If it is set to 16 bits, the obtained data seems to exceed 16000000.

It seems that it is output with 24 bit data, but I do not know in what frmat the number is being output.

It is EVM data, please refer to attached data.

DDC 1128 16 bit output setting, FPGA also 16 bit setting.

---

I appreciate your great help in advance.

Best regards,

Shinichi