Other Parts Discussed in Thread: SN74HCT373

Hi-

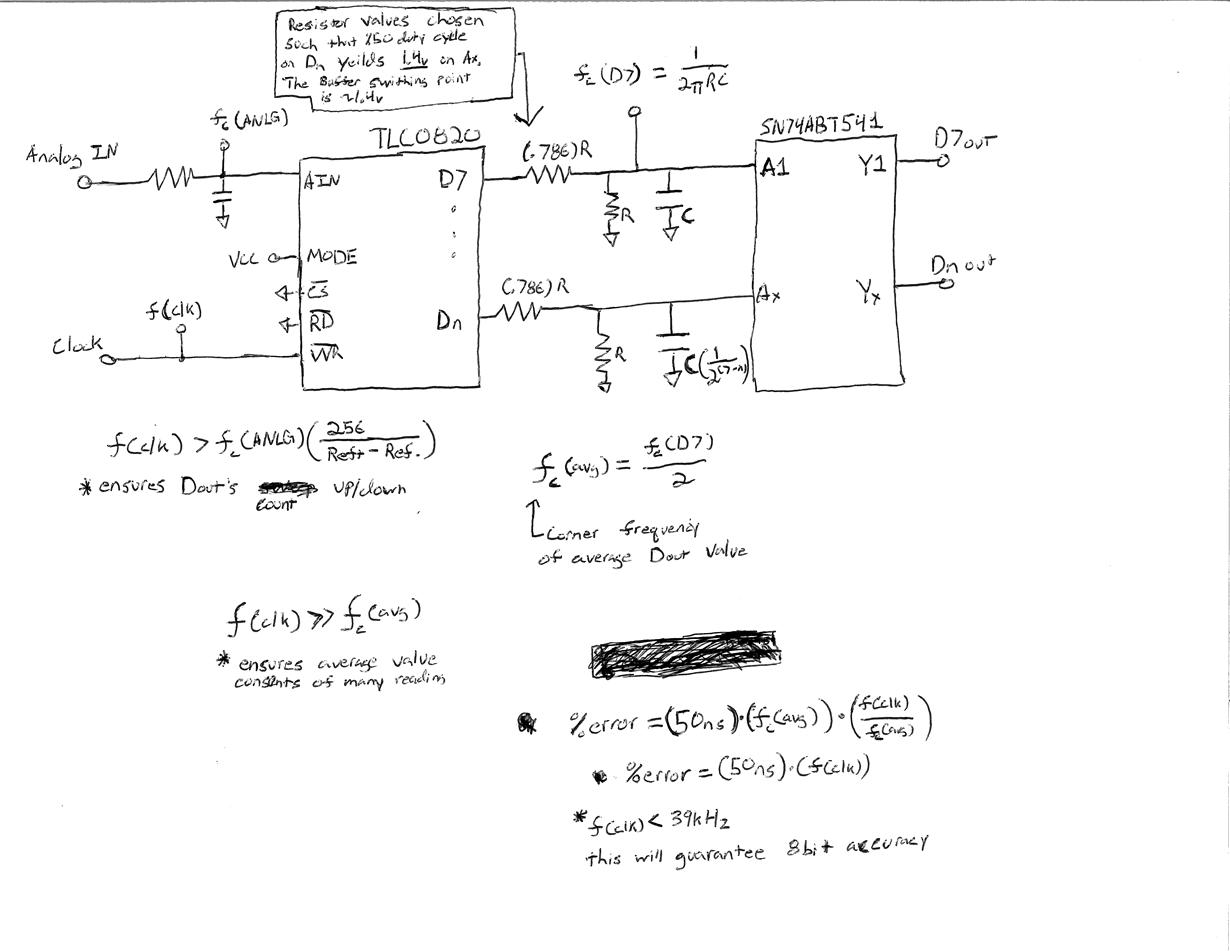

I am looking at using a TLC0820 ADC.

I am trying to minimize external the components needed to control the ADC conversion.

I have 2 requirements:

Use 1 control signal (The control signal will be slow, 10kHz max)

Avoid the tri-state output.

Will the following control set up work?

Thanks

Tony.