Hello

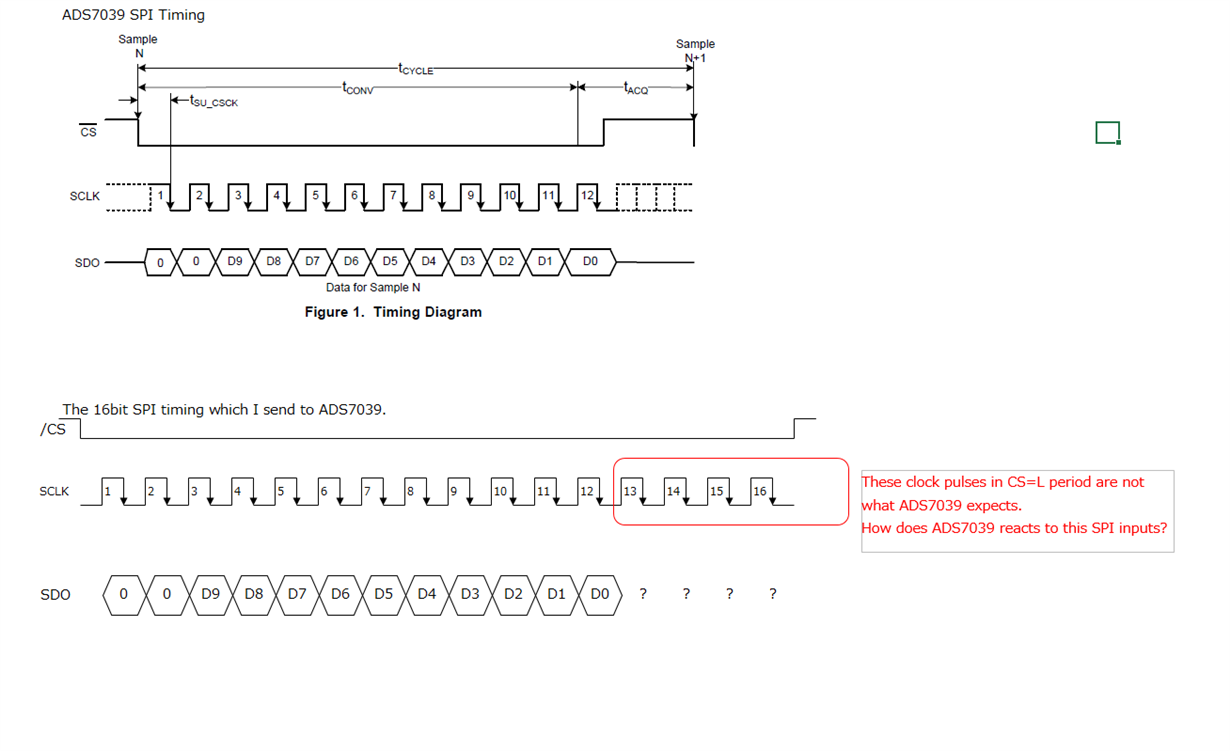

I will have to input 16 SCK clocks to ADS7039, during the period of /CS=L,

as shown in the diagram, because of the restriction of the SPI function of my processor.

Now I wonder how does ADS7039 react to these extra SCK pulses.

Can ADS7039 output correct data with the leading 12 pulses anyway, so that we can just ignore the last 4 bit data?

Thank you very much in advance.

Ryuji Saito