Other Parts Discussed in Thread: DAC39J84

Hi,

I am using Xilinx FPGA KC705 to do DSP and transmit the processed signal together with I,Q signal by DAC39J84.

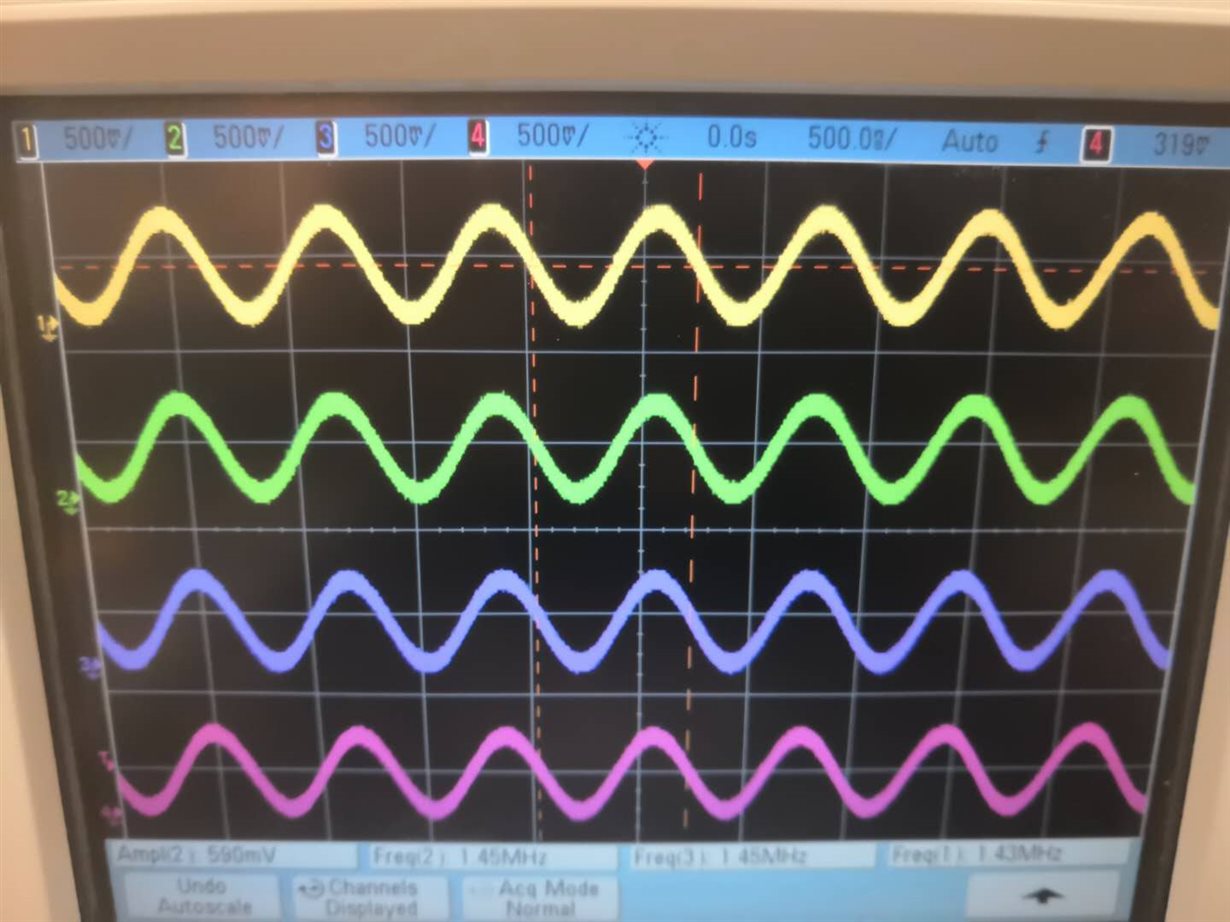

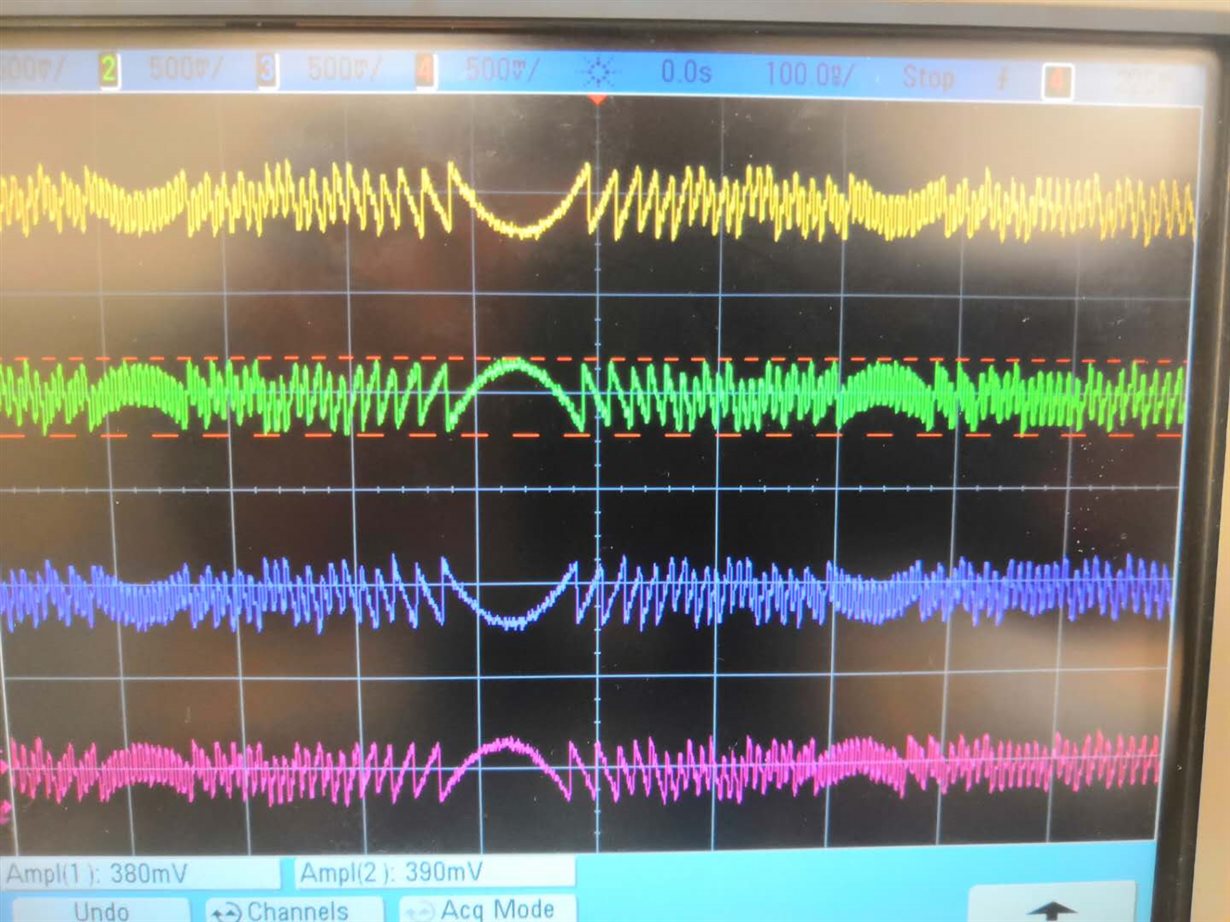

In the first stage, I plan to interface FPGA with DAC in JESD204 standard to transmit a sine wave.

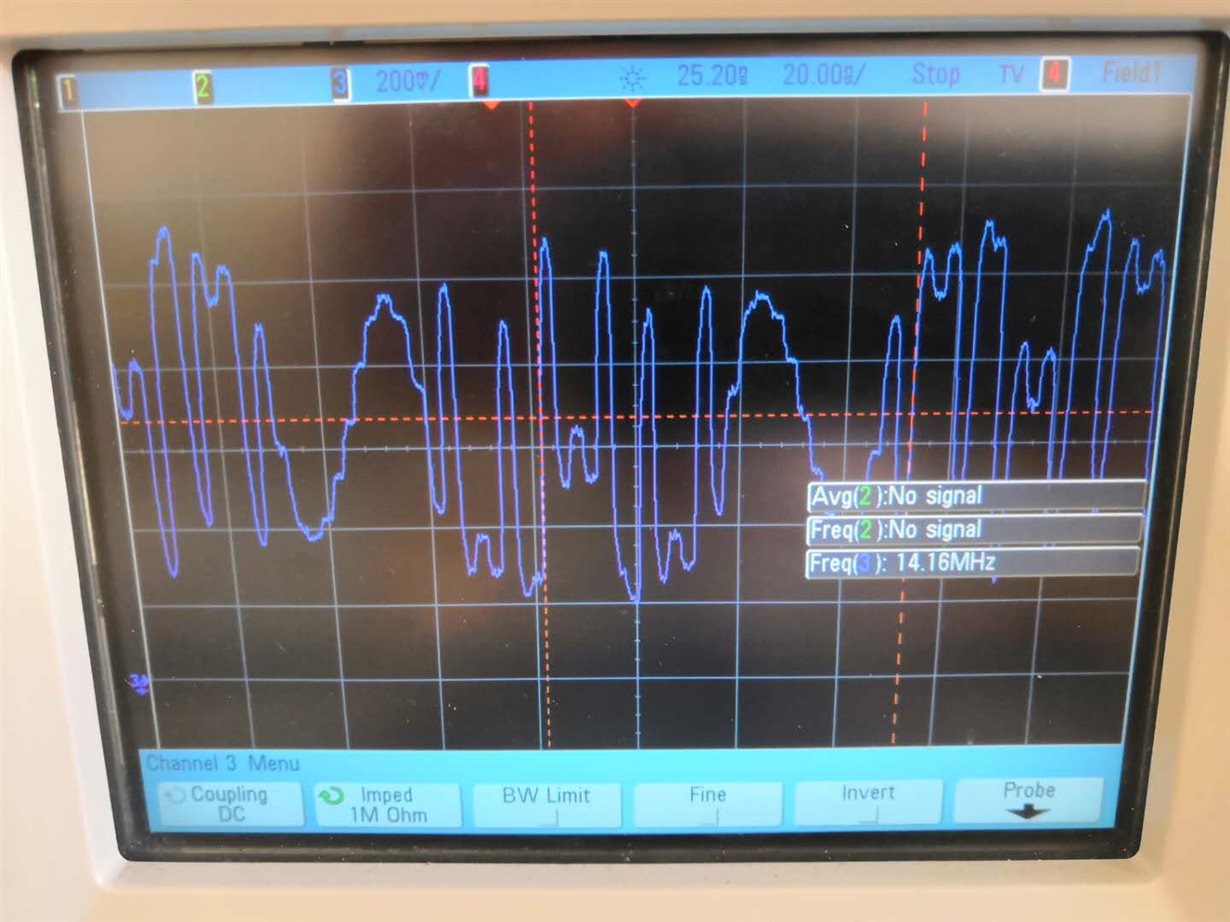

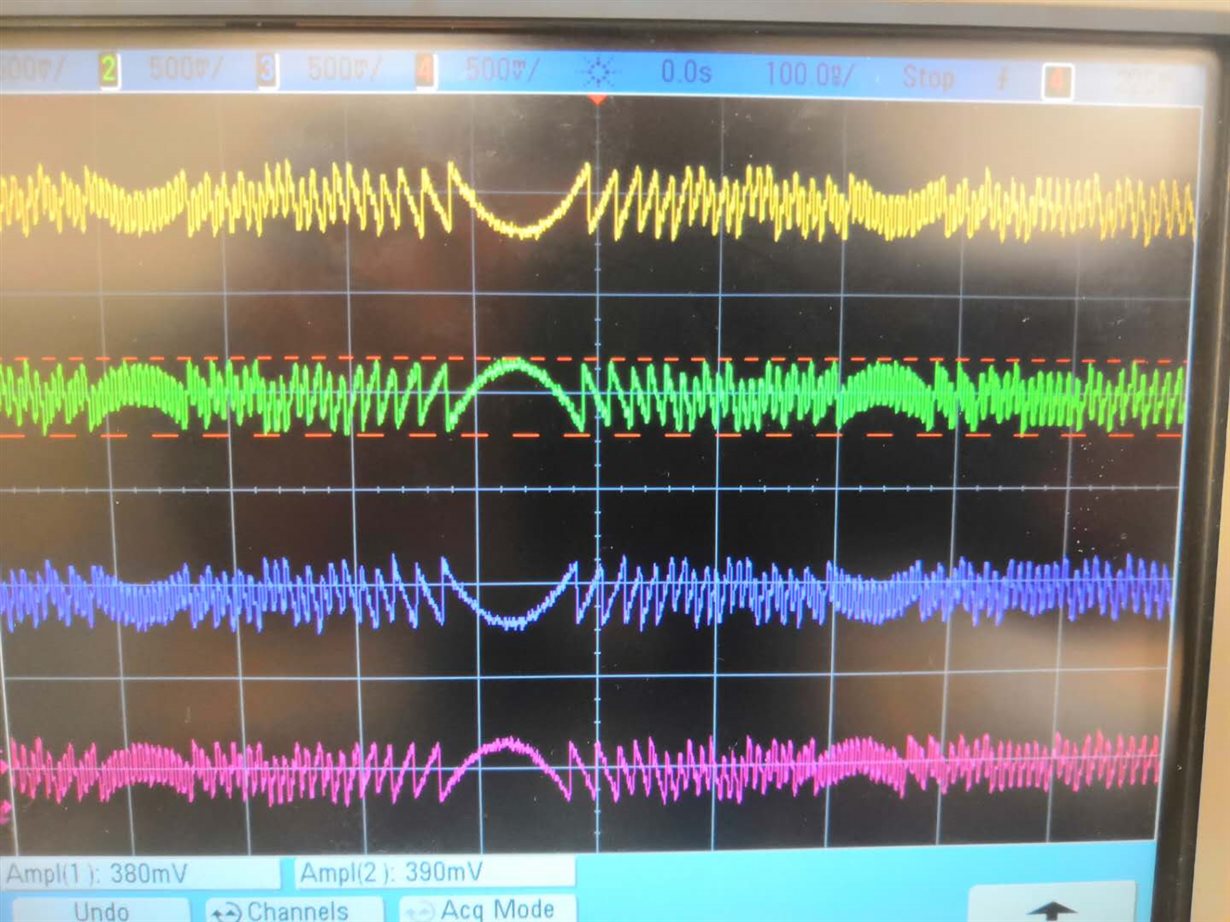

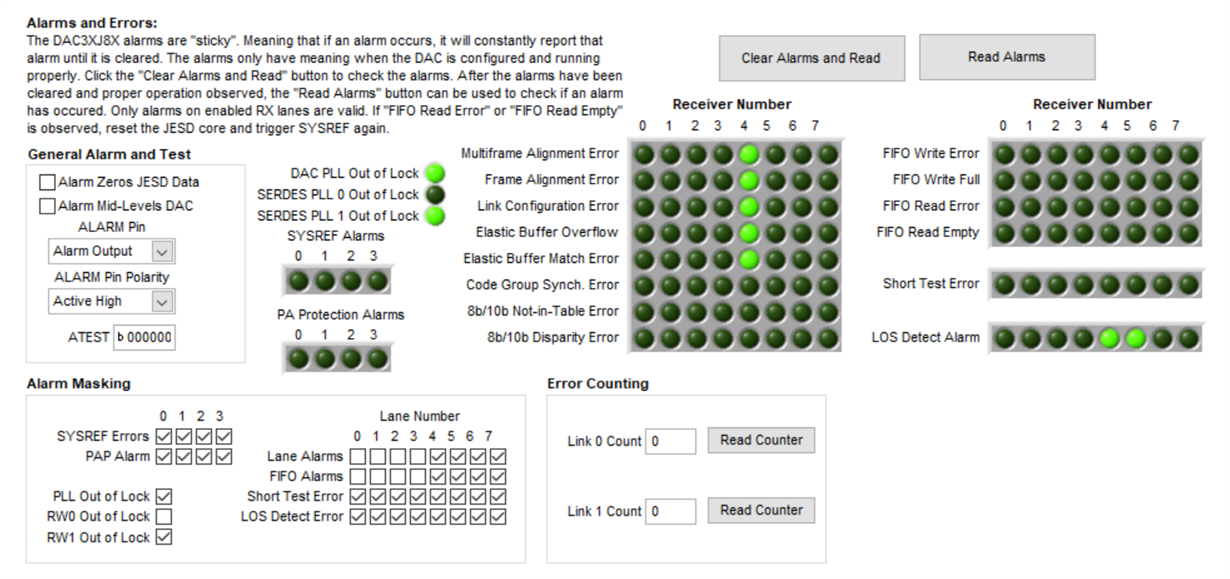

So far the link sync is achieved. But I received distorted signals from the DAC even though I matched all the configuration parameters.

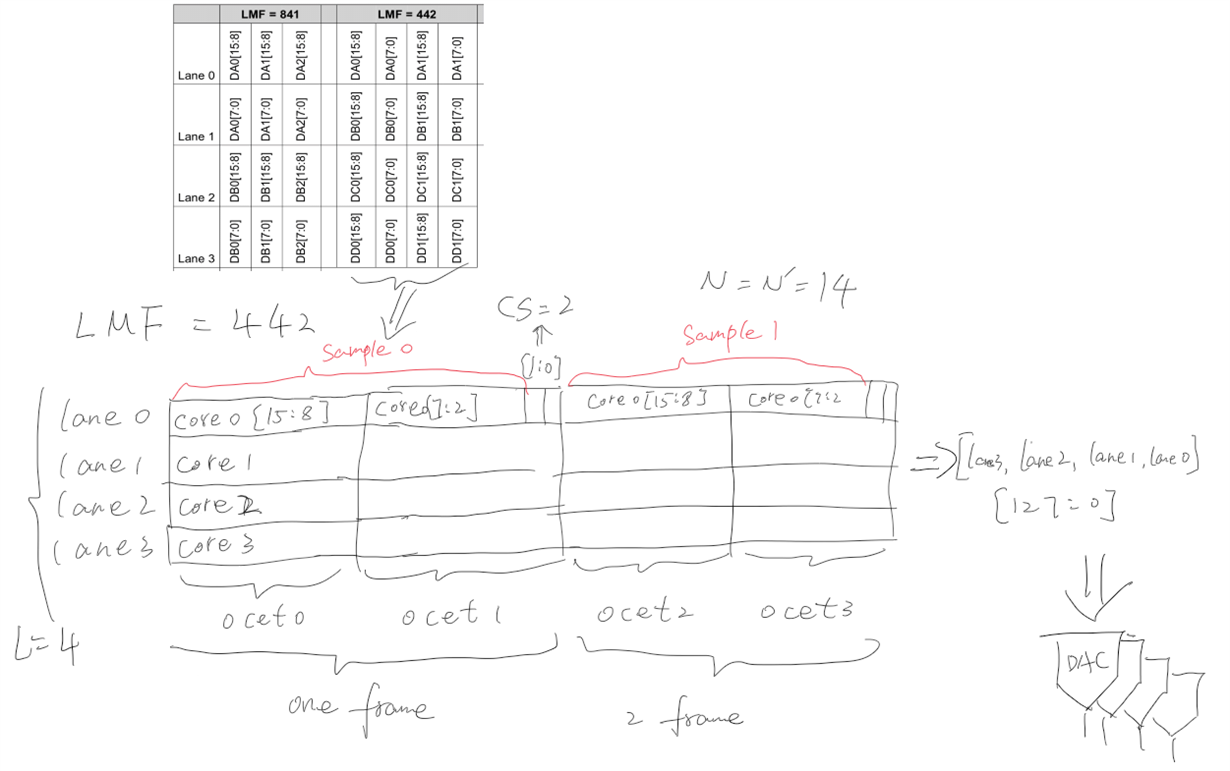

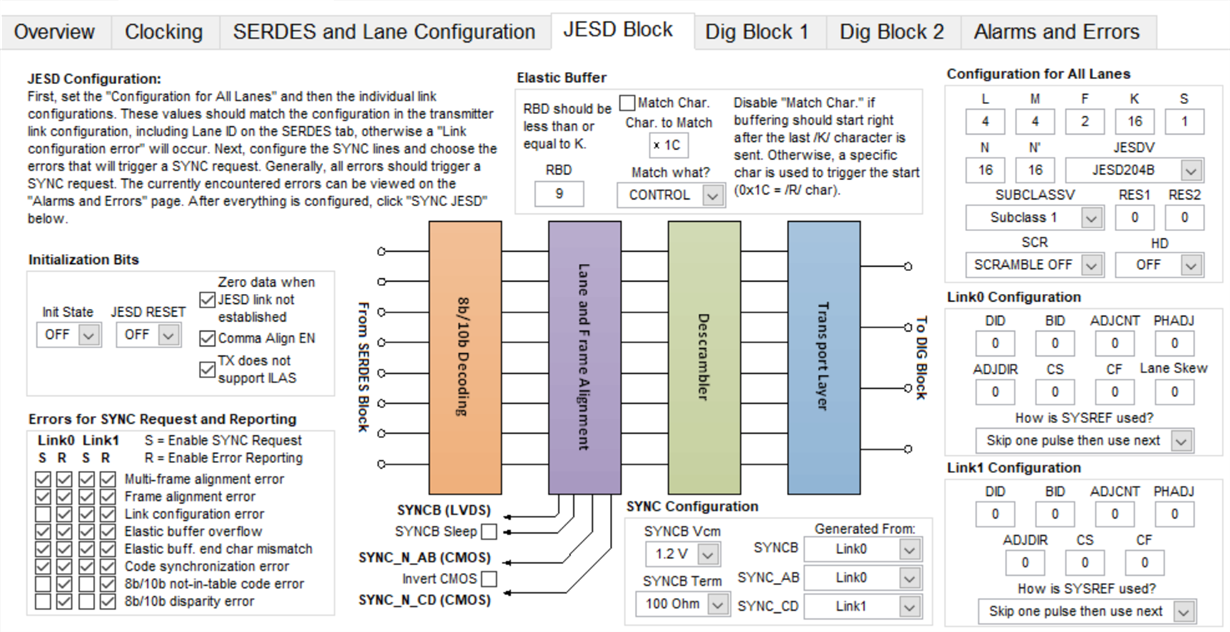

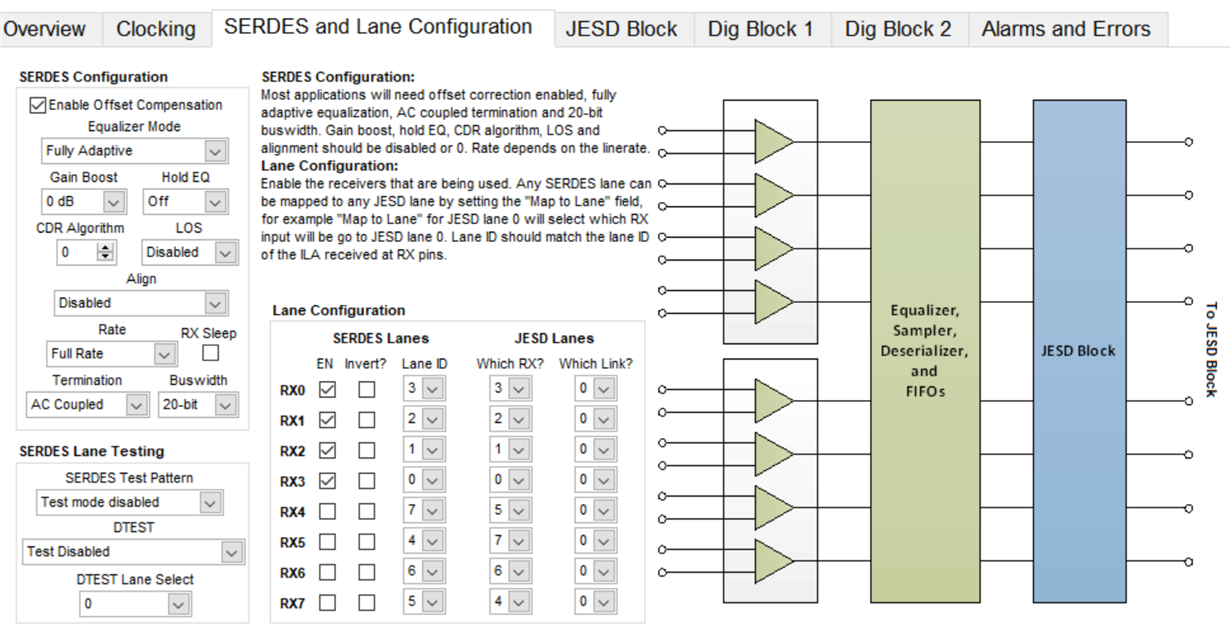

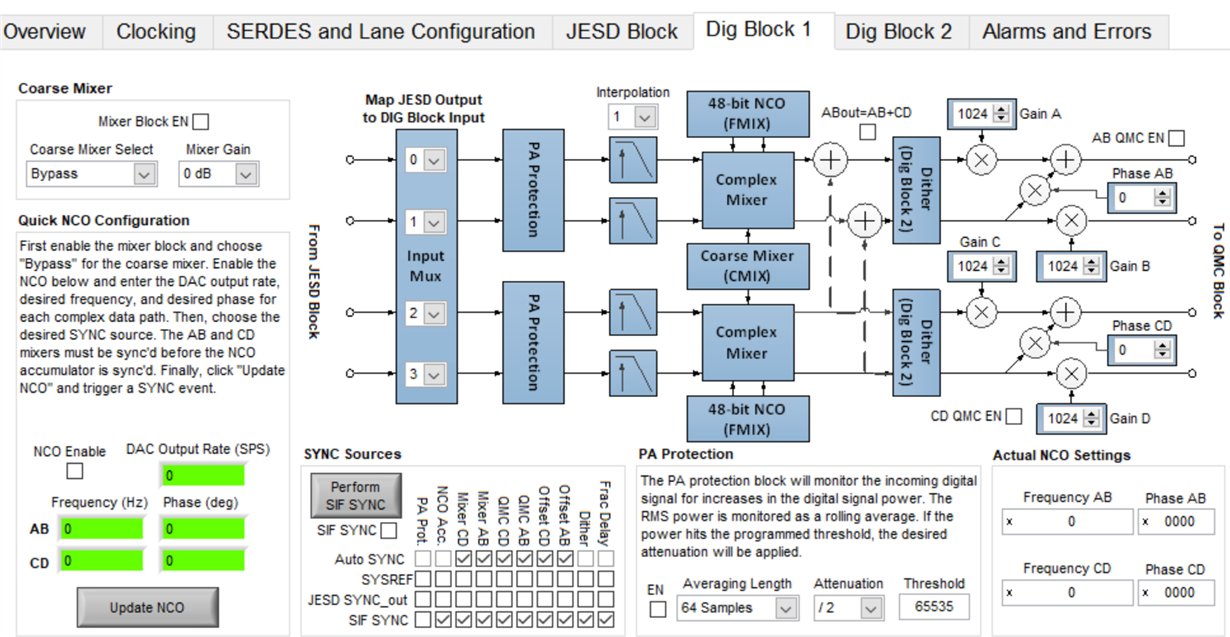

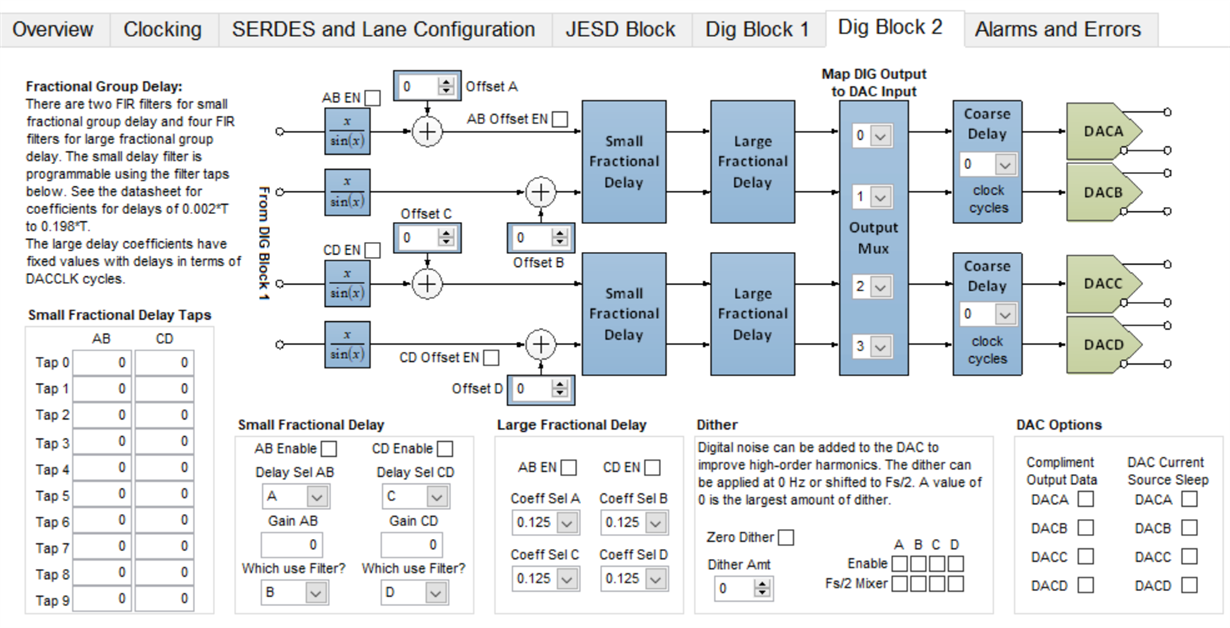

LMFS =4221 K=16 I set these in DAC GUI

And I wrote the corresponding register values to JESD core in FPGA

Addr x008

Data x0000_0001 Enable Lane Alignment

Addr x00C

Data x0000_0000 [0] Disable Scrambling

Addr x020

Data x0000_0001 F (octets per frame) = 2

Addr x024

Data x0000_000F K (Frames per multi) = 16

Addr x014 Tx Only

Data x0000_0003 [7:0] ILA multiframes = 4

Addr x814 Tx Only

Data x000_0100 [12:8] s=1

Addr x810 ILA config 4

Data x0010_1004 [20:16] N'=16 [12:8] N=16 [7:0] M=4

Could anyone give me some suggestion about what could be the potential problems ?

Thanks for any help.