Hi!

Part A:

When I use ADS112C04, I met some problems.

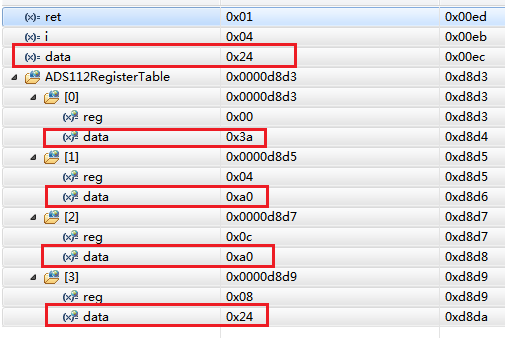

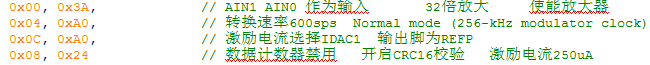

1 Configure 4 registers(Reg0~Reg3) through I2C

write Reg0:0x3A //

write Reg1:0xA0 //

write Reg2:0xA0 //

write Reg3:0x24 //

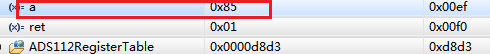

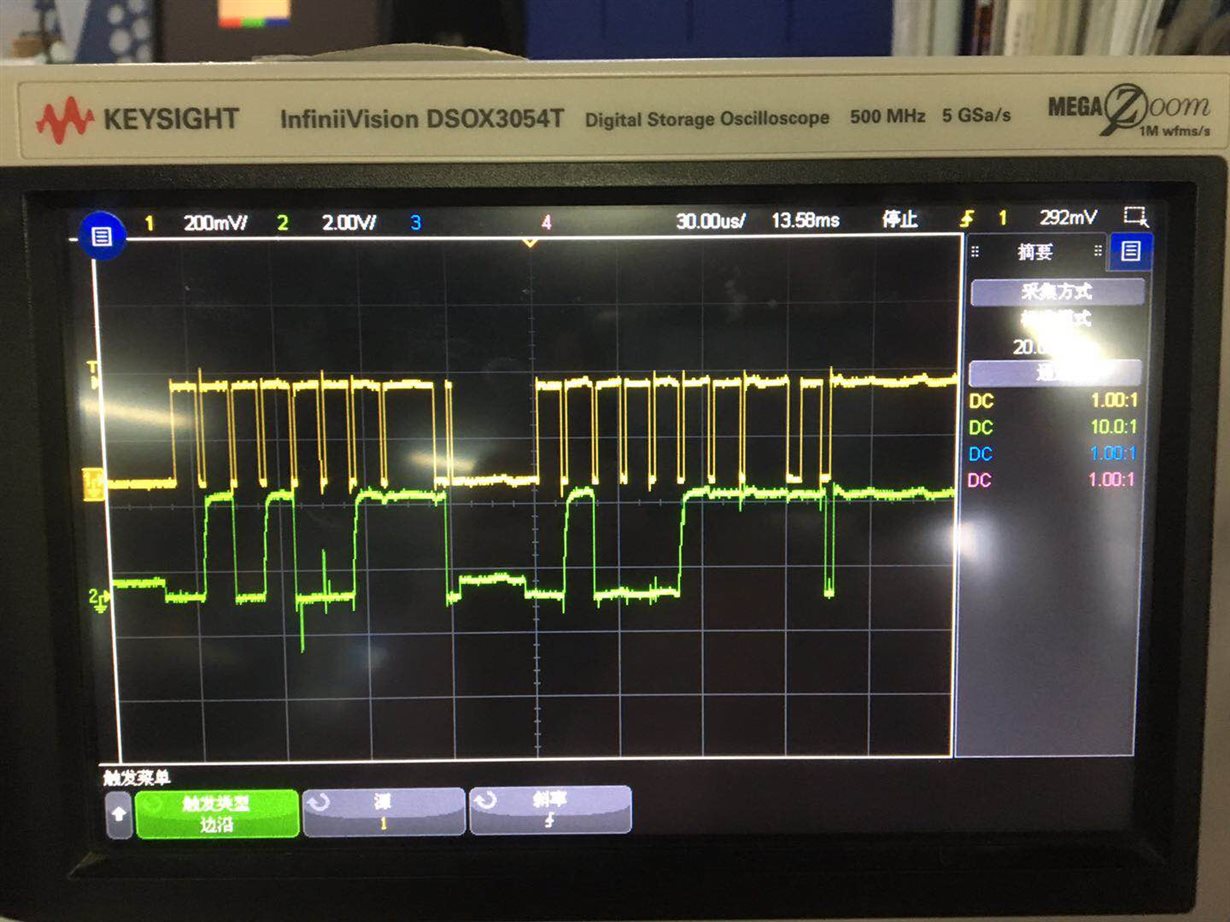

2 All 4 registers read and write normally in first time. then I read the register again, it's failure that the value is different with the first time and the AD samples is wrong.

you can see the figures as follow, please help to analyze.

Part B:

As described above. I have another problem. Do you have the recommended configuration? And is the configuration order required ?

BRs,

Barret