Hi all,

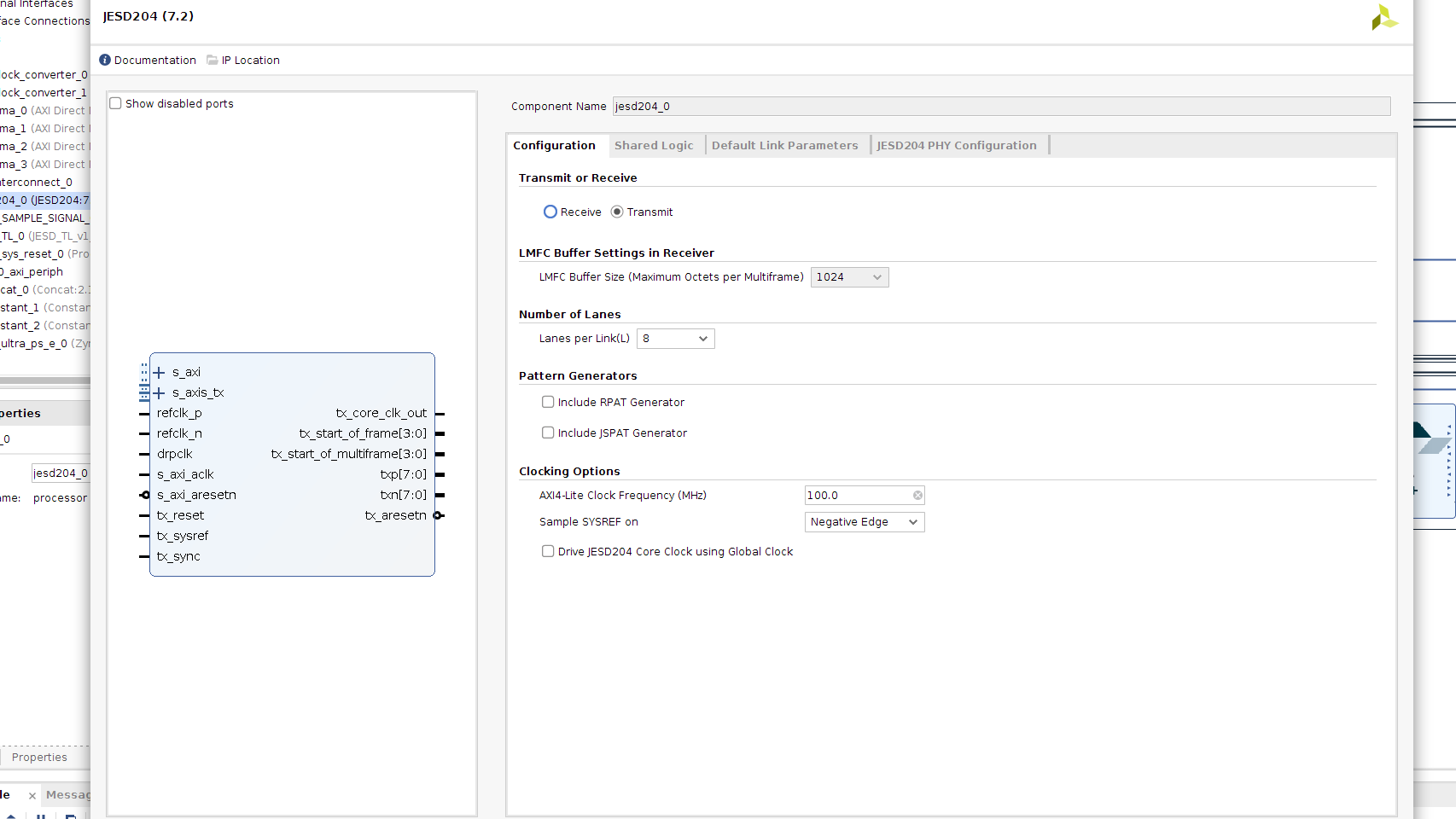

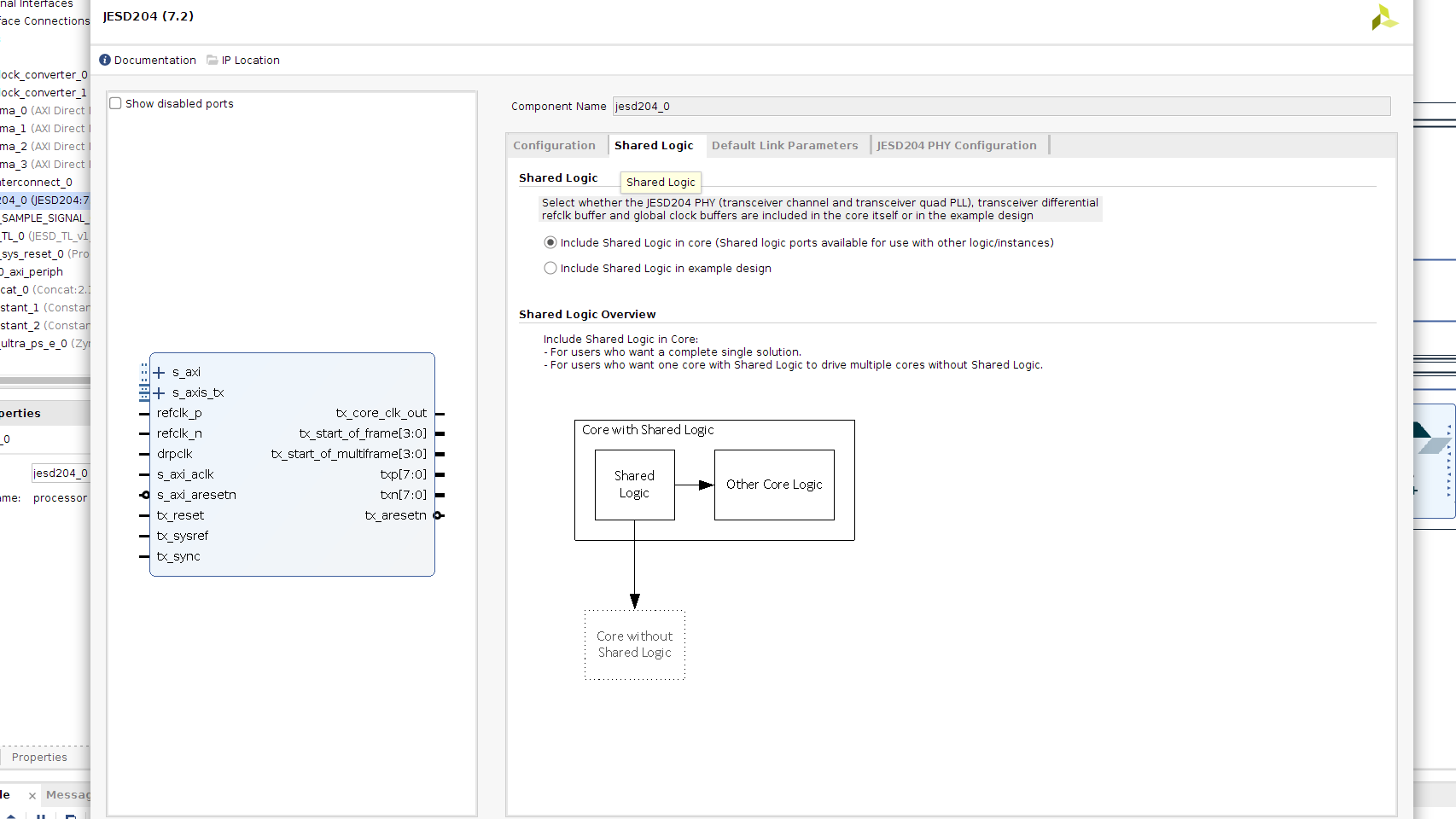

I am trying to send data to DAC39J84 from Ultrascale+ JESD block.

My design works fine with the evaluation board (http://www.ti.com/tool/DAC37J84EVM)

However, on the custom build board the SYNC signal from the DAC is not performing as expected.

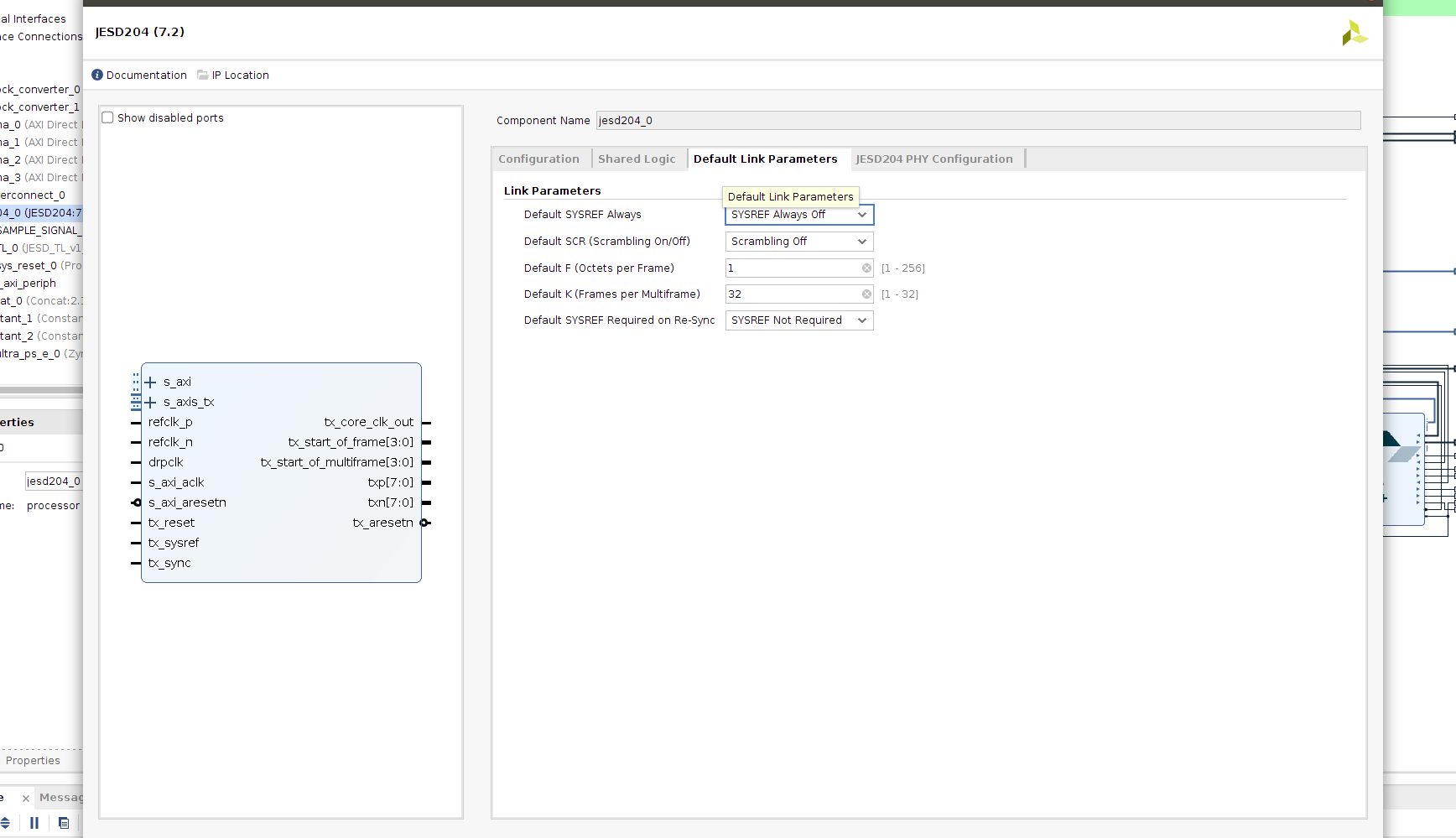

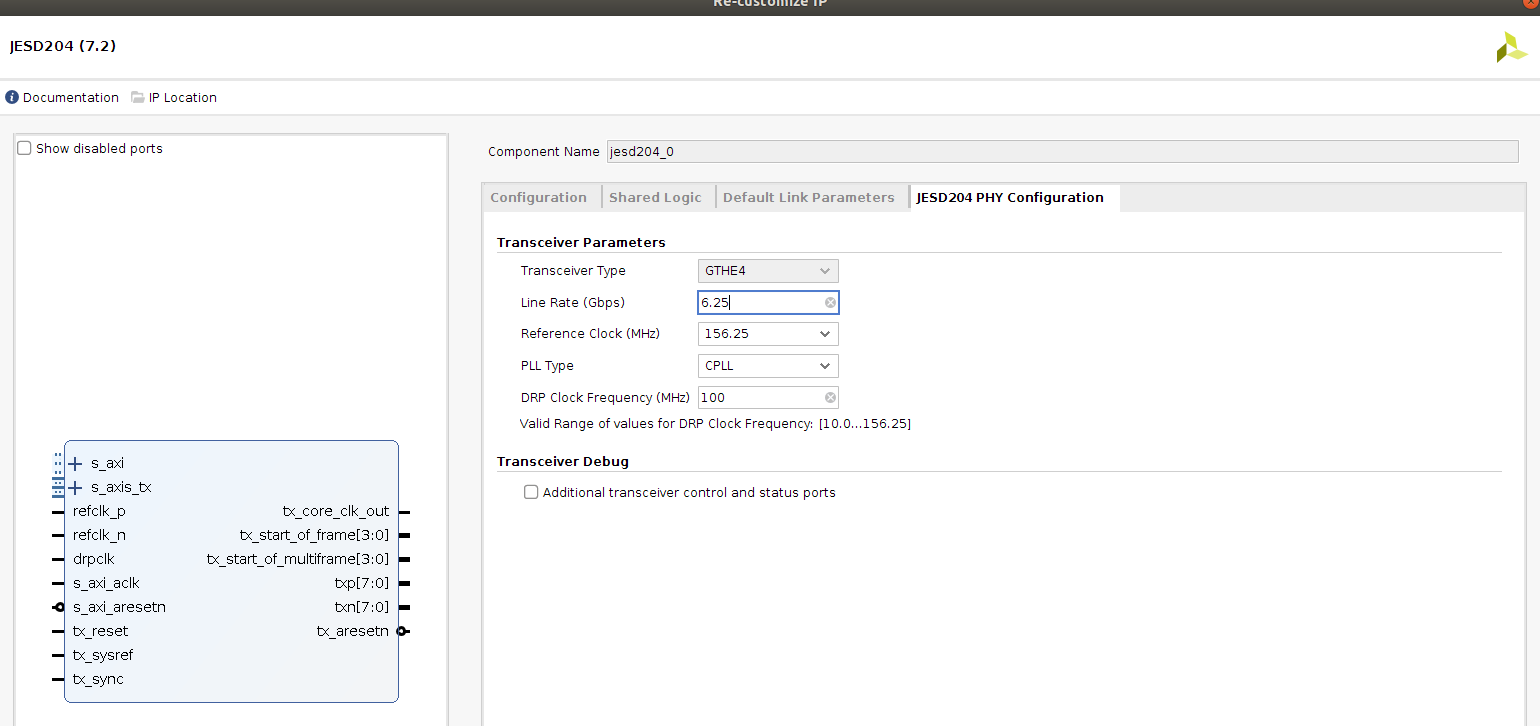

My JESD design: subclass1, 8 lanes, F = 1, K = 20, Line rate = 6.25 GBPS, Reference clock = 156.25, Sysref = 4.88 (sysref is same for DAC & FPGA), DAC clk = 625 Mhz.

Again, the design works fine on the eval board and the layout of the custom board is very similar. I checked clocks and spi configuration of the DAC and clock distributor (LTC6951) they operate as expected and voltage levels are ok.

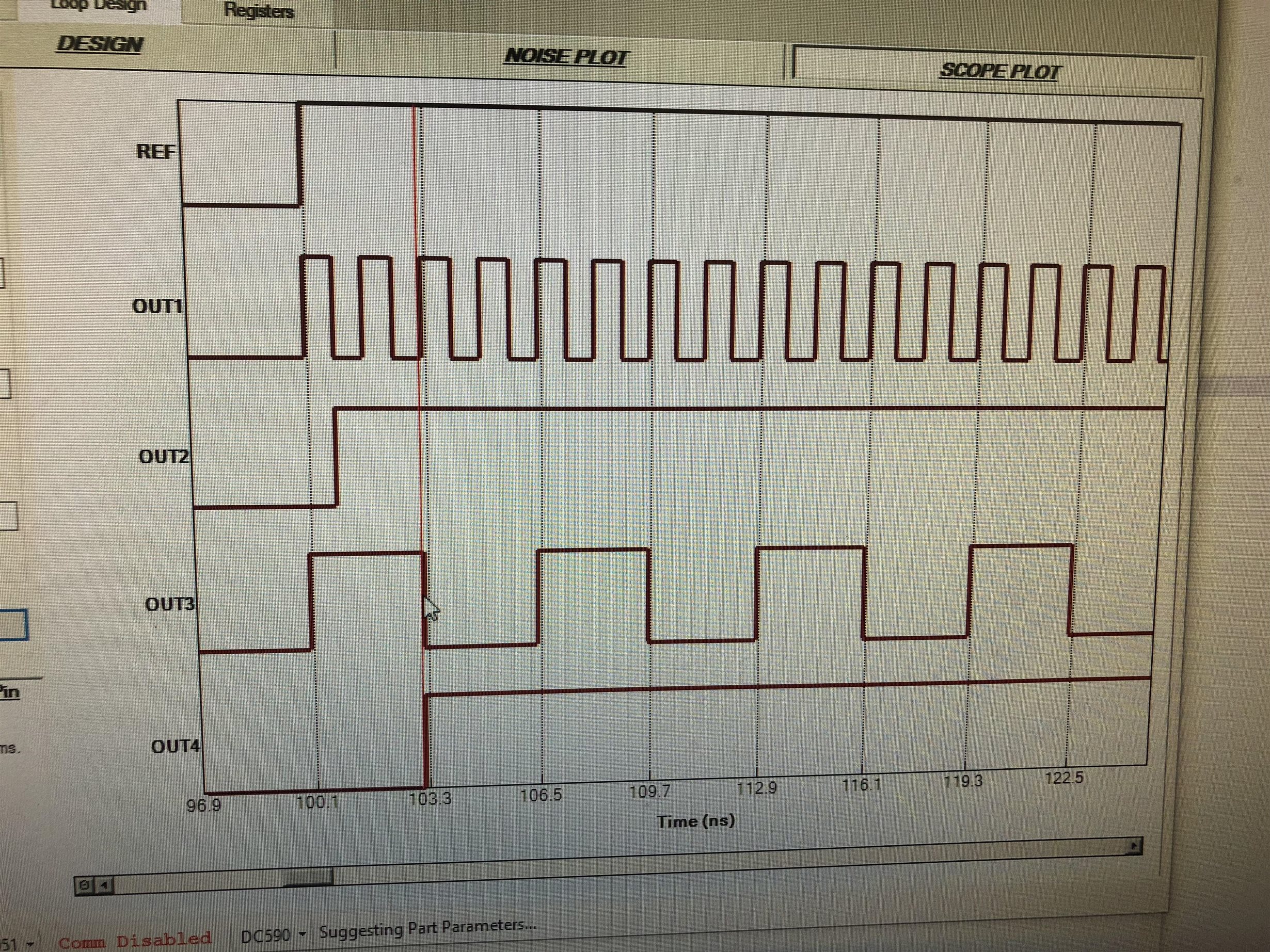

Clocks:

OUT1 -> DAC clk = 625MHz

OUT2 -> DAC SYSREF = 4.88Mhz

OUT3 -> FPGA Refclk = 156.25Mhz

OUT4 -> FPGA SYSREF = 4.88Mhz

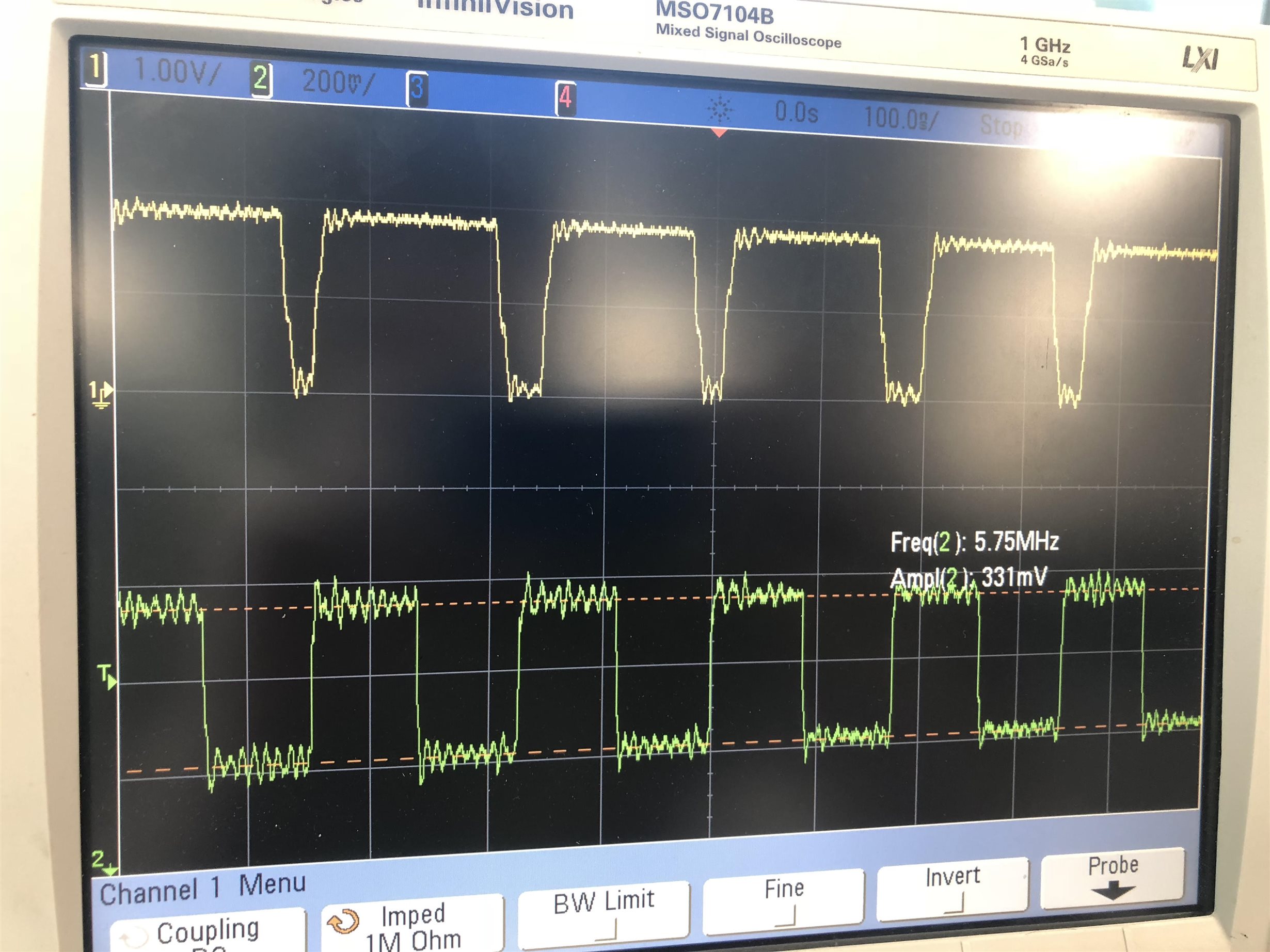

This is what is happening on the eval board (top -> SYNC; bottom -> sysref):

On the custom board SYNC is always high and I am not sure what can cause that. Apparently, its a popular problem:

https://e2e.ti.com/support/data-converters/f/73/p/574027/2131081?tisearch=e2e-sitesearch&keymatch=DAC39J84#pi320995=4

https://forums.xilinx.com/t5/Networking-and-Connectivity/JESD-RX-sync-not-asserted/td-p/892775

This is the flow:

1) Program clock distributor and align outputs (it supplies dac clk and FPGA clk; both SYSREF clocks are muted)

2) program FPGA

3) program DAC (here SYNC goes high and will never change)

4) supply SYSREF for ~ 1 sec (here SYNC pin should start toggling)

5) NOTE: JESD IP core can see the sysref as it assers tx_tready pin

Also, what does SYNC need to toggle? is it looking for SYSREF edge or K28.5 symbols?

Any ideas?