Part Number: ADS1675

Hello,

I am debugging a DAQ-system consisting of four ADS1675 that are expected to sample and output data simultaneously but do not. I measure deviations in arrival time of DRDY of around 10 .. 100 nanoseconds. The parts are configured in High-Speed LVDS mode and running continuously at full speed 4 MSPS. Data on outputs is correct (correspond to analog input).

START is synced to falling edge of CLK and pulsed for 3 CLK cycles before being held high.

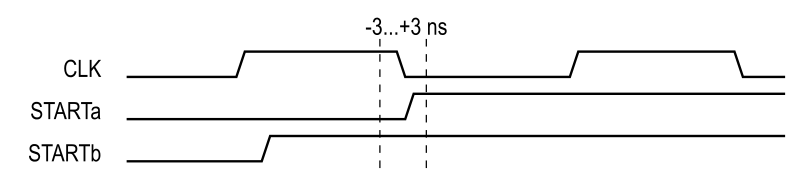

1. In the datasheet (SBAS416D) under TIMING REQUIREMENTS: High-Speed LVDS on page 7 is a setup requirement for SYMBOL tSTCLK given by -3..3 ns. How should one understand a maximum setup time?

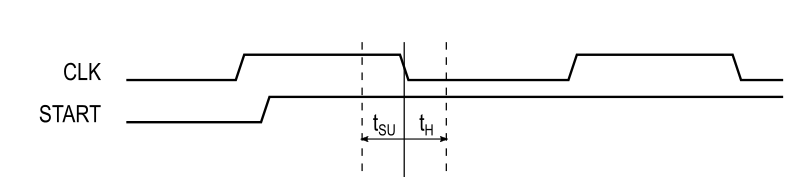

2. Under TIMING REQUIREMENTS: START on page 9 is a minimum setup time of 0.5 tCLK to rising edge given, which is in contrast to point 1.

Do you have an idea why data output is not synchronous? What is the achievable or typical deviation of DRDY output time between multiple synced ADS1675s?

Regards.