- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear Hall,

Christopher Hall (1528318) My adc working fine, but i have problems writing in the register yet still I'm able to get the converted data. Please check my previous comment. I got 3 questions to be addressed. Kindly help me with the same. waveshare adc

Question 1: The values which I'm writing in the status, adcon, drate registers doesn't match with the values which I read after 100ms in the same registers.

But the values which I write in the MUX register matches and I've verified it by varying dynamically. Kindly help me with the problem.

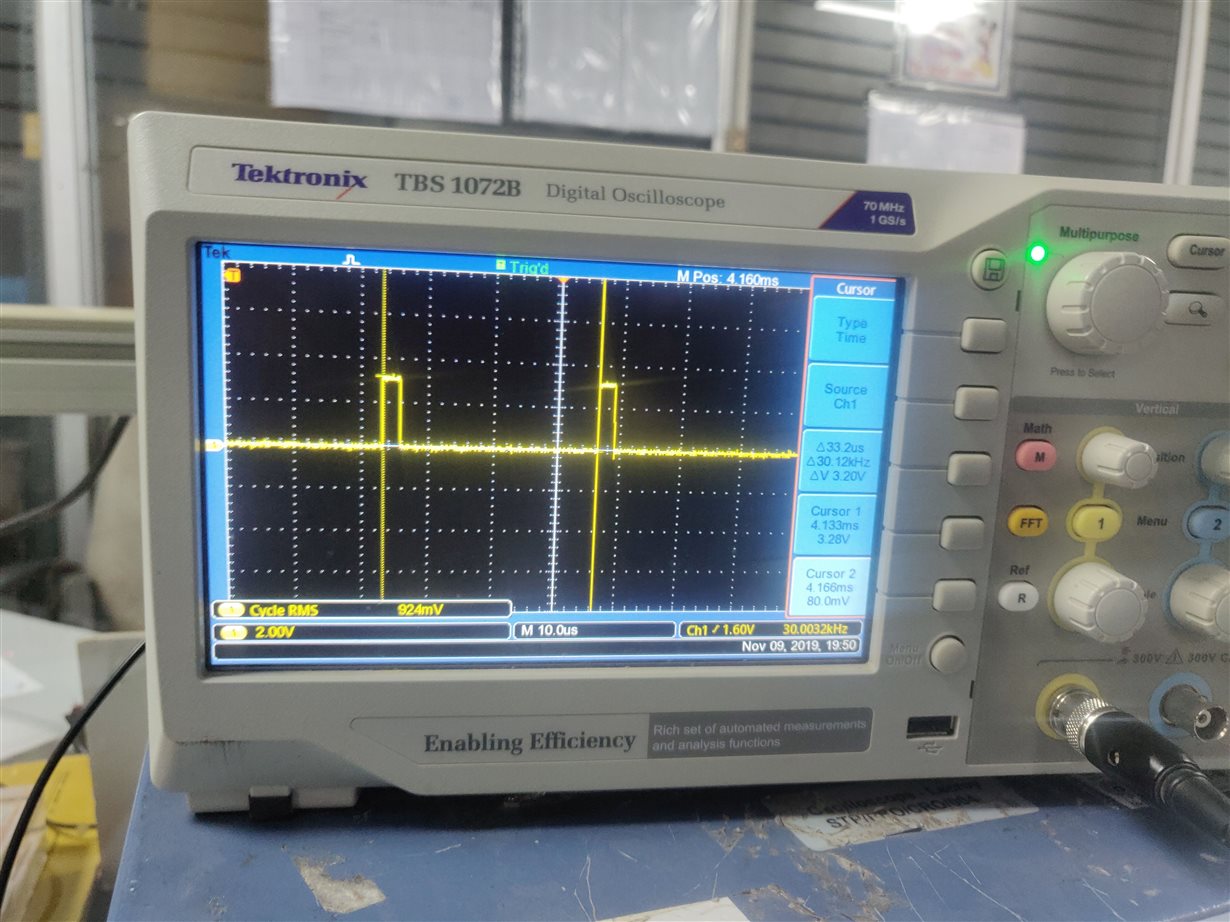

Question 2: The drate value defaults to 0xF0(since drate value is not updating when I write on it) which is 30ksps and I've verified that value with my drdy signal in an oscilloscope.

The problem is when I give an input as sinusoidal signal of frequency 1Hz(time period = 1sec) I get only 2.8k samples for a sec.

My assumption is that if I set as 30ksps then for a sine wave with time period of 1sec should get 30k samples, but when I read the samples I get only 2.8k samples. I've set my spi clock frequency is 2MHz. Please correct me if I wrong.

What should I do to achieve at least a minimum of 10k samples ?

Question 3: How to use RDATAC command? If possible share a snippet of your code that involves rdatac command. Should I check for the drdy signal to go now or will update automatically?

Hi Gokul,

See my responses below.

Best regards,

Bob B

Gokul Balasubramanian said:Part Number: ADS1256

Dear Hall,

Christopher Hall (1528318) My adc working fine, but i have problems writing in the register yet still I'm able to get the converted data. Please check my previous comment. I got 3 questions to be addressed. Kindly help me with the same. waveshare adc

Question 1: The values which I'm writing in the status, adcon, drate registers doesn't match with the values which I read after 100ms in the same registers.

But the values which I write in the MUX register matches and I've verified it by varying dynamically. Kindly help me with the problem. [Bob B] Please give us detailed information at to what you are writing, what you are reading and the 4 channels of oscilloscope or logic analyzer data to go with it (CS, MISO, MOSI SCLK). If a single MUX register appears to be working, what you are doing differently when setting and reading back the status, adcon and drate registers? Are you writing these registers as a group? Or are you writing these registers individually? We really need to see the communication to be of any further help.

Question 2: The drate value defaults to 0xF0(since drate value is not updating when I write on it) which is 30ksps and I've verified that value with my drdy signal in an oscilloscope.

The problem is when I give an input as sinusoidal signal of frequency 1Hz(time period = 1sec) I get only 2.8k samples for a sec.

My assumption is that if I set as 30ksps then for a sine wave with time period of 1sec should get 30k samples, but when I read the samples I get only 2.8k samples. I've set my spi clock frequency is 2MHz. Please correct me if I wrong.

What should I do to achieve at least a minimum of 10k samples ? [Bob B] Here again it would be helpful to see if you are able to capture every sample by showing the DRDY signal and your communication in an oscilloscope of logic analyzer output. How often you capture will depend on what else your micro is doing. If you are using a polling loop most likely you will drop data. It is best to use DRDY as an interrupt so that every conversion is captured.

Question 3: How to use RDATAC command? If possible share a snippet of your code that involves rdatac command. Should I check for the drdy signal to go now or will update automatically? [Bob B] The RDATAC command simply puts the conversion data on the output bus. You will still need to send SCLKs with dummy transmit data to capture the result. You still need to monitor DRDY to know when new conversion data are available. What you gain with the RDATAC is you do not need to issue the RDATA command (24-bit transfer instead of 32). But you can receive corrupted data if the update takes place in the middle of the read of the previous conversion. So you need to take care of question 2 before using RDATAC.

Dear Bob,

I'm using (STM32F302R8 mcu and Waveshare adc) for interfacing. Schematic:https://www.waveshare.com/w/upload/2/29/High-Precision-AD-DA-board.pdf

I'm writing 4 registers separtely with wreg command followed by 0x00 as my second command byte. Below is the table of what I write and what I receive in return. Kindly verify. I've also attached the SCLK MOSI and DRDY signal for your reference. For more details about my code and other specifications, you can go through this link. http://e2e.ti.com/support/data-converters/f/73/p/855591/3177628#3177628 Kindly read my previous comments to get a precise idea of my situation. Thank you for the quick reply.Christopher HallBob - HPA Dallas Payne I'm setting 2MHz clock.

| Registers | Written value(HEX) | Read value after 500ms(HEX) |

| Status | 0x06 | 0x30 |

| Adcon | 0x20 | 0x20 |

| Drate | 0x82 | 0xF0 |

please note: My mux register is updating where as the rest doesn't. Adcon value constants to 0x20 even if I wirte another value.

I'm using polling method, yet 2800 samples is very less when I set as 30k samples. Please suggest some ideas to improve my data collection on my mcu side.

Question 1: How can I verify if adc is converting with 30ksps?

Question 2: Is it possible to read 10k samples within a single time- period region of a signal(continuously)? If yes, kindly elaborate.

Question 3: Is it possible to determine the frequency of the signal from the adc output(without using FFT)??

PLease address the register problem too.

Can you please share snippet of your RDATAC code. Sorry for the long post!

Hi Gokul,

Unfortunately a 2-channel scope is not very valuable when looking a a 4-channel communication. Do you or can you get access to at least a 4-channel oscilloscope so I can see your communication write and read of the registers? We need to verify that you do not have a code issue, so the only way we can verify the response from the ADS1256 is to see the actual communication.

The first picture you show appears to be a register write to the MUX register using AIN0 for AINp and AINCOM for AINn. As this is the communication you have said is working, I'm not sure why you sent this communication instead of one that isn't working. However you said the SCLK frequency is 2MHz. According to the scope plot the horizontal time base is 25us per division. Between each division there is less than 3 clock periods. If we assume that there is 3 SCLK periods in 25us time, the SCLK frequency is actually 120kHz. If we assume no code latency, the best number of samples you could capture is 5ksps. So here is one of the answers to your capture question.

The answer to question 1 is in picture 2. To determine the output rate you measure the time between 2 DRDY pulses. The scope delta is showing 30kHz which would be an output data rate of 30ksps.

The answer to question 2 is yes, but perhaps not with the system or setup you are using. This is not an issue with the ADS1256, but rather with the system you are using. I'm not sure how much further help we can be as this is a code/system issue.

For question 3, yes it is possible to determine a frequency by capturing data points contiguously (not missing any conversions) and plotting in a time domain. You can then determine the number of conversions from the start of one cycle to the beginning of the next. The frequency is 1/(number of samples * period of one conversion). You also need to consider the Nyquist theorem as well for determining the maximum frequency that can be determined.

For register reads, you must make sure you are following the t6 timing requirement of the SPI timing diagram shown in Figure 1 on page 6 of the datasheet. If you send a command you must allow it to decode and setup the DOUT before issuing any further SCLKs. RREG command is one of the commands that requires this delay.

Your last question is about RDATAC. RDATAC is a command and is transmitted as one byte. I believe what you are really asking for is the code to read the data from the device after the RDATAC command has been issued. This is an SPI function call and really a code snippet from a TI device will not help when using a ST micro. The usage is as follows when DRDY transitions from high to low state:

You must complete the entire communication before the next DRDY transition or you will receive corrupted data. As you are already having timing issues, the use of RDATAC will only make things worse so I highly discourage the use of RDATAC until you can guarantee the communication timing.

Best regards,

Bob B

Dear Bob,

First of all I really thank you for your speedy reply. Unfortunately I dont have a oscilloscope that captures 4 channels. That SCLK image might be the old one. I've verified the clock and it is around 2.2MHz. I've tried to capture the MOSI and clock signals during the status adcon and drate transmission. I also give t6 time delay, infact a little more than t6 itself. Christopher Hall Bob - HPA Dallas Payne

I found an another interesting fact today (i.e) even before writing the status, adcon and drate registers value, I find a burst of periodic DRDY signal of freq 30KHz and I've attached the signal for your reference. Can you please explain this situation.

Regarding that frequency calculation, Thank you it really did help. But the thing is most of the time I'm missing the conversion data (i.e) most of the time my no. of samples is incorrect. Is my period of conversion is 1/drate if not please correct me.

Algorithm to find number of samples: I took one random sample value converted it to volts and added a offset of ±0.001v to it and incremented the count value by checking the condition in a if statement. if(sample > sample - 0.001 && sample < sample - 0.001). Is my algorithm ok? WAVEFORMS.rar

I'll share my test result : I've connected a 1Hz signal in ain0 and set mux as 0x0F with aincom = grnd.

Most the times my number of samples was 2500 to 2900 which gives a frequency of 10Hz approx.

I've calibrated my system in all my know possible ways. (i.e)

Mcu clock speed = 72MHz,

SPI clock speed = 2.2MHz

Using DRDY as interrupt.

Using RDATAC

For code latency please check my previous comments in ADS1256:ADS1256 thread, which I mentioned earlier.

Question 1: What more can I do to optimize so that I wont miss my conversion data during frequency calculation?

Question 2: Even before the start conversion(sync and waveup command) I find DRDY getting low(burst signal shared in the above waveforms.rar file). Is that even possible?

And again sorry for the long post!

Hi Gokul,

You are attempting to do too many things at once and due to the fact you do not have the proper tools for troubleshooting you should only look at one issue at a time. Let's start simply by reading and writing registers. Send me scope shots of writing 1 register and then reading it back. As you only have a 2 channel scope you will have to repeat the test twice. Once showing the SCLK and MOSI and the second with SCLK and MISO. I will try to interpret the diagrams to see if communication is working as expected. This will be difficult for me, but I will give it a try. Previously the SCLK frequency was too slow, so we need to also verify this as well.

Best regards,

Bob B