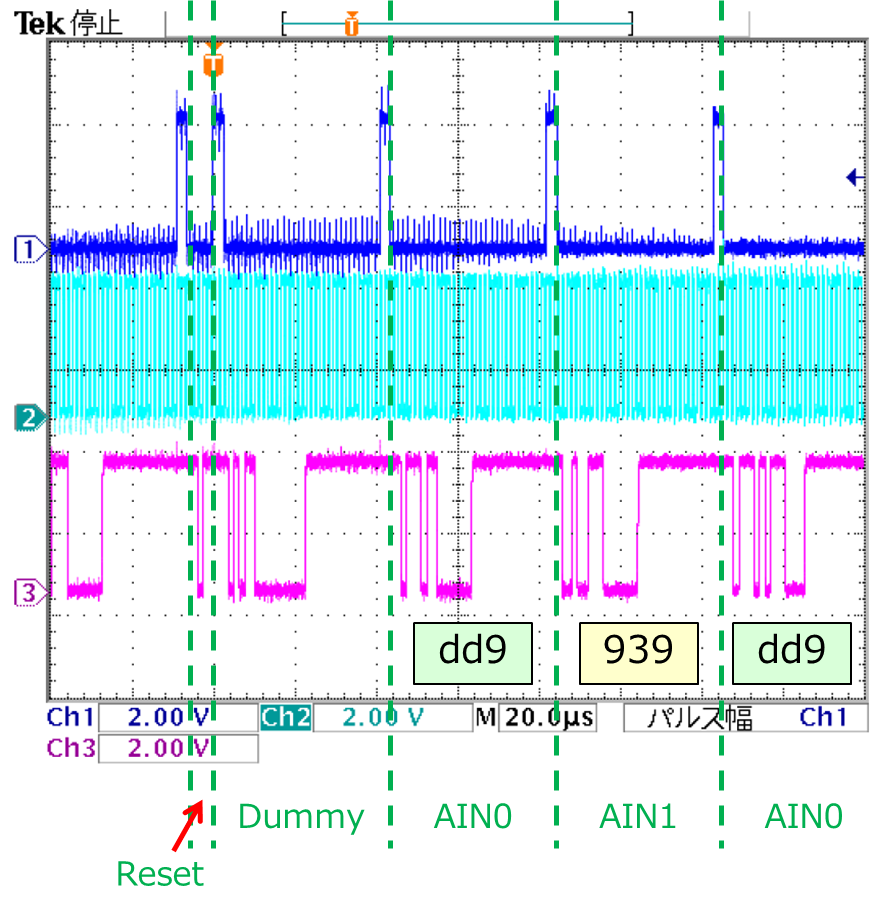

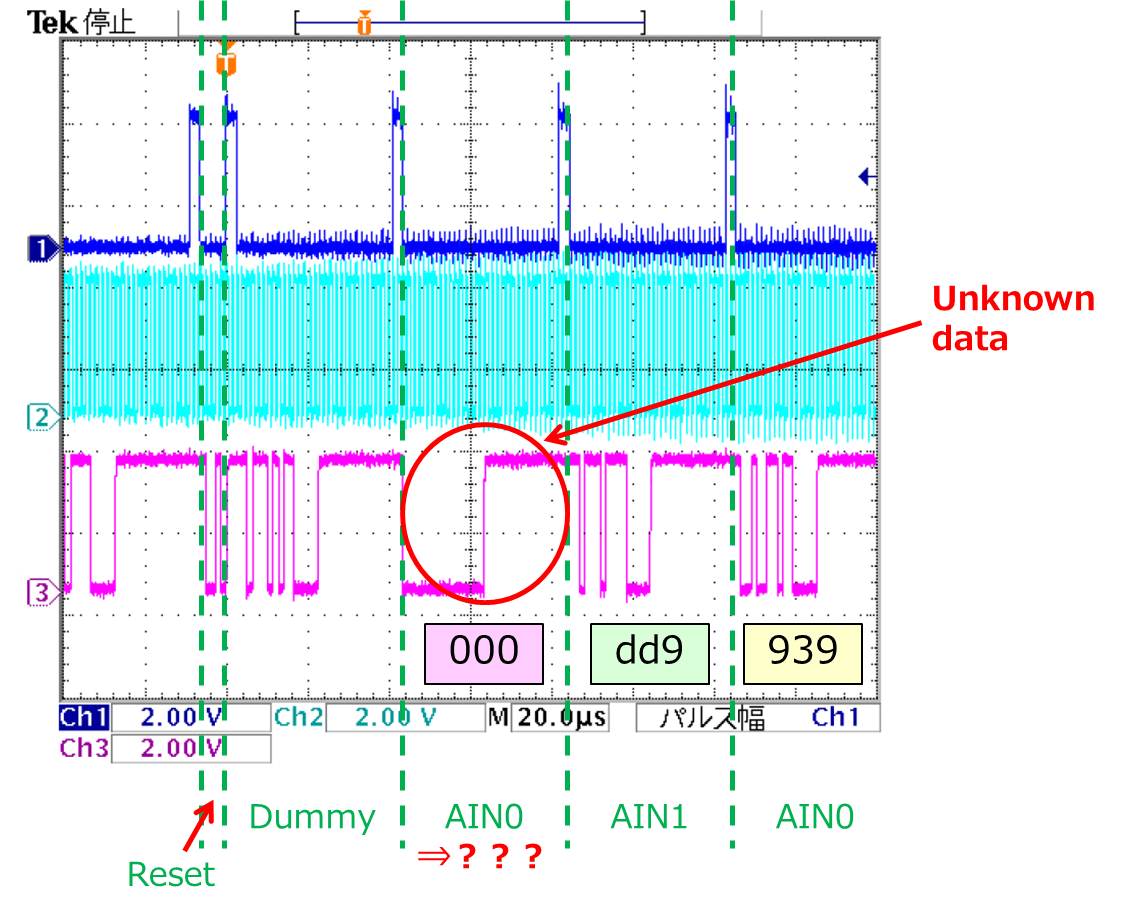

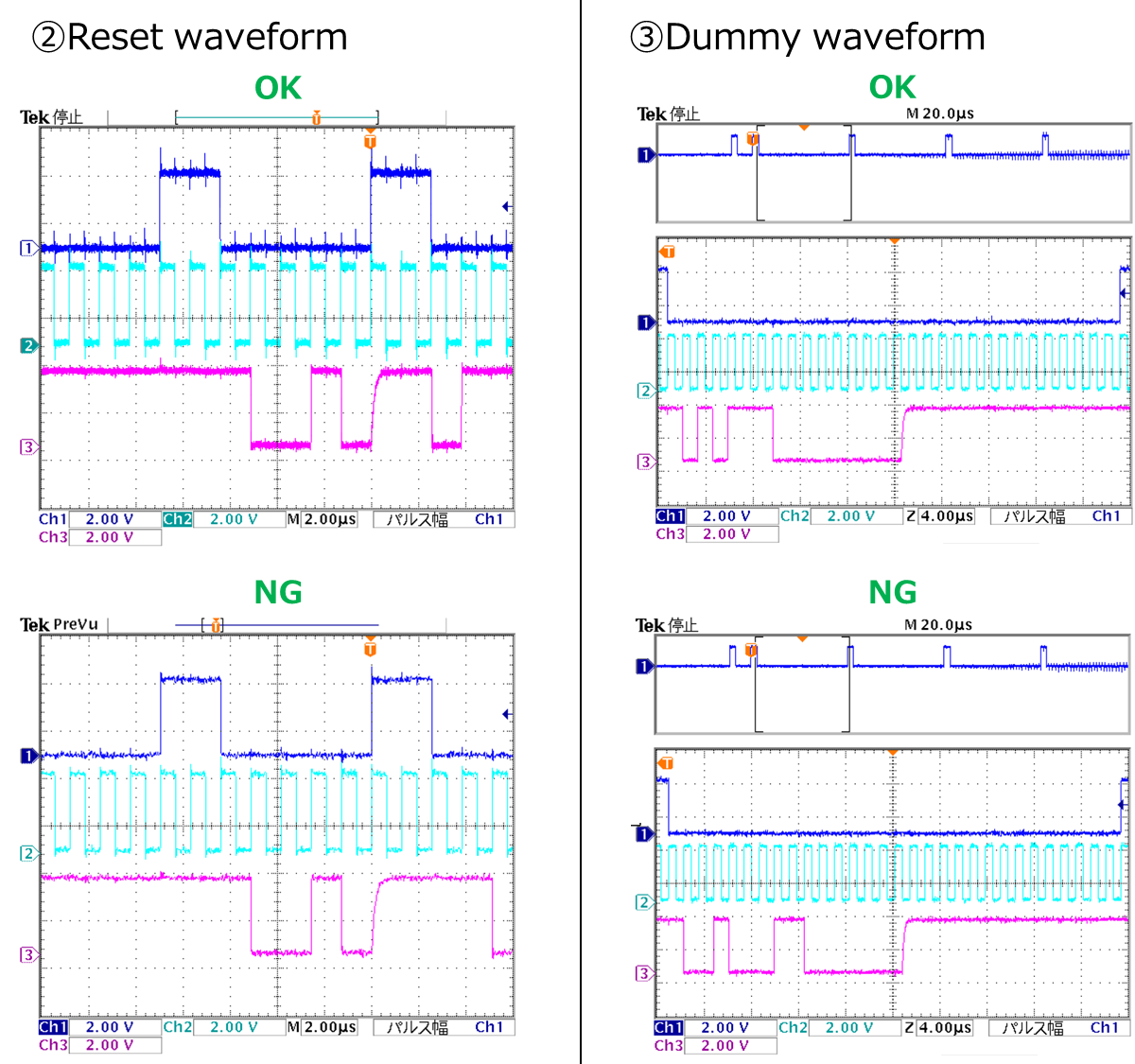

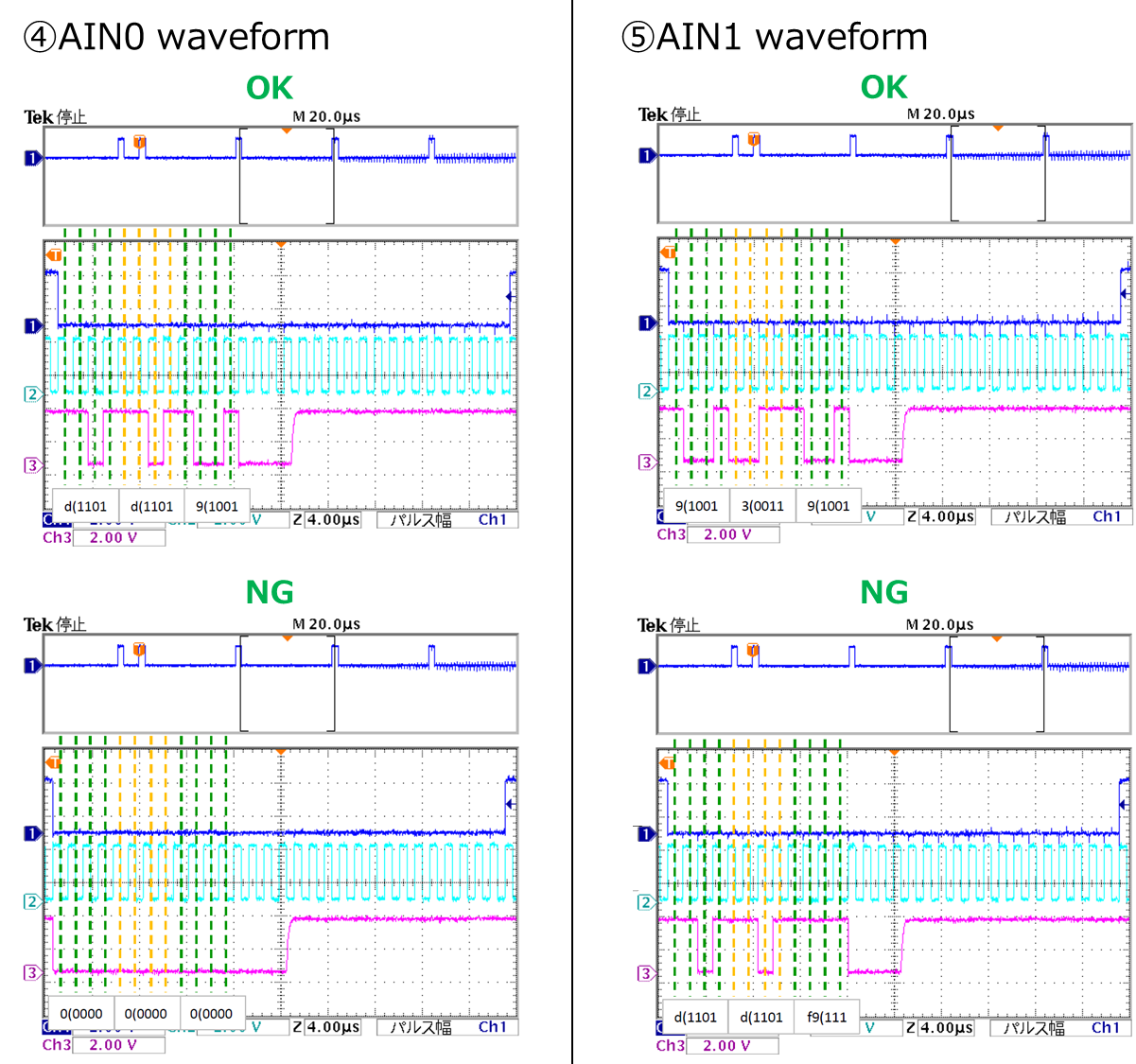

About TLV2542, certain probability occur output data error; reversed ch0 and ch1.

Please let me know about the reason and measure.

【Condition】

・This error occur 9 per 200 of TLV2542 board.

・When 9's error TLV2542 are changed frequency below, 781.25kHz was only error.

⇒100KHz:OK, 500KHz:OK, 781.25KHz:NG, 1MHz:OK, 1.5152MHz:OK, 2.778MHz:OK, 5MHz:OK

Is frequency relation for above error?

・Vdd: 3.3V, Vref; 2.5V

Best regards,

Satoshi