Hi Guys,

I am a student working in a testing class. I am trying to test one Digital to Analog converter TLC7524 in a testing project. I downloaded the datasheet and I am trying to understand the datasheet. I am confused about several questions:

1. "electrical characteristics over recommended over recommended operating free-air temperature range, Vref=+-10V, OUT1 and OUT2 at GND". Does that mean that OUT1 and OUT2 need to be grounded when I test the parameters?

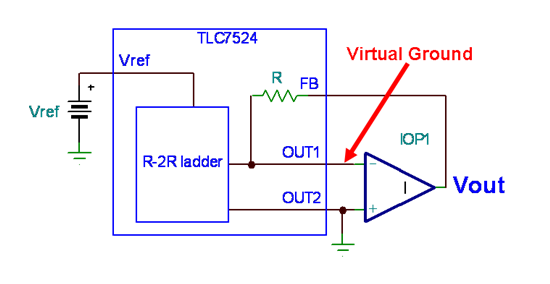

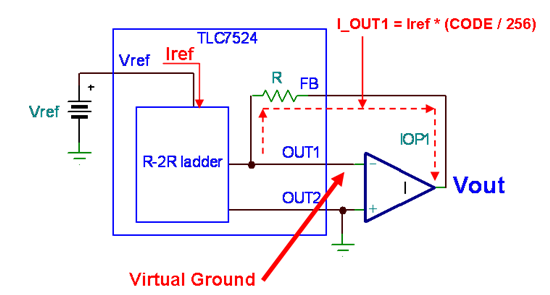

2.I don't understand how OUT1 and OUT2 work. It is said that the binary-weighted currents are switched between the OUT1 and OUT2. Does it mean that the analog output will appear at OUT1 or OUT2 depending on different digital input codes? But in the unipolar operation and bipolar operation diagrams, the OUT2 is always grounded.

3.What is RFB exactly used for? In principles of operation, RFB is connected to a resistor Rb and then connected to the output of an amplifier. Between Rb and OUT1, there is a capacitor. It is said that the Rb and C are only used under some conditions. Does that mean if the application is not in some condition the Rb and C don't need to be used and the pin RFB is just connected to the OUT1 and the output of the amplifier?

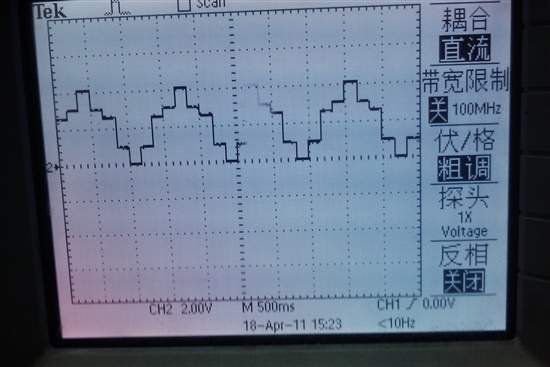

4. One amplifier is used to generate the output. Is it necessary? If it is necessary, what type of the amplifier is appropriately to be used? We don't use this device in a specific application. We just want to get some reasonable analog outputs from this DAC. Could you give us some recommendation?

5. This DAC consists an inverted R-2R ladder. So the analog output should be inverted, such as if the Vref is positive, the analog out should be negative. Is it correct? But in the unipolar operation, there is an inverted amplifier connection in the output termination. So the final output of this application should be positive, is it right? However, in Table 1, the analog output is negative.

6. In Page 4 of the datasheet, Note1 says Cext = 13pF. The Cext here is the capacitor in the diagrams in Page 7?

By the way, I am also looking for a IBIS model of this device. Is there anyone who has or knows where I can get it or a IBIS model which is similar to this part? Could you please answer those questions? I will greatly appreciate it.

Thanks and have a good day,

Yihong

Hi Tony,

Hi Tony,