Dear Technical Support Team,

I'm testing DAC7568ICPW (C grade / Gain=2) with noise.

VOUT shows half voltage after applying noise(IEC61000) to power supply line.

Q1.)

Can you inform me the cause of the DAC output being halved?

Q2.)

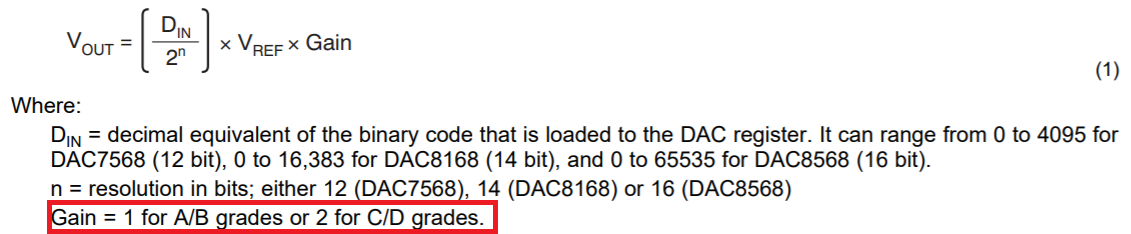

According to the datasheet , Vout formula is below. Gain is fixed by grade.

AVDD=5V and Internal VREF=2.5V then Gain=2 and output range is from 0 to AVDD

AVDD=5V and Internal VREF=2.5V , then Gain=1 and output range is from 0 to AVDD/2

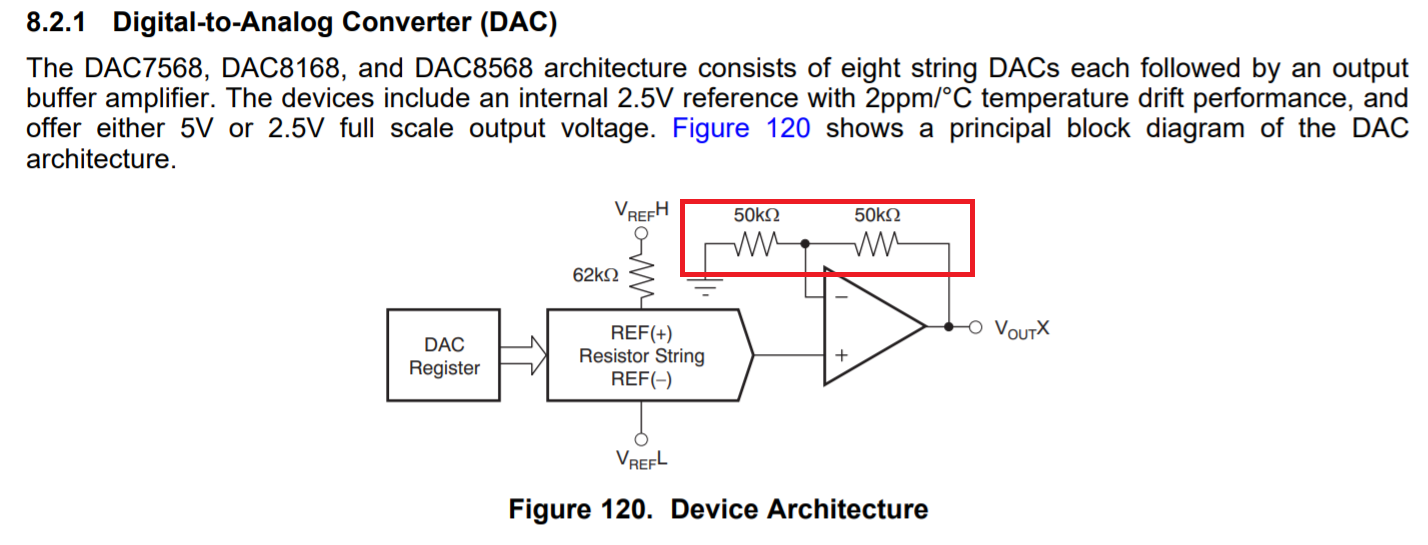

And figure 120,I guess that both resistance 50kΩ of output amp set Gain=2 for C/D grades and A/B grades has no 50kΩ resistance for buffer amp(Gain=1).

Is it correct?

3.)

Is it possible to change GAIN=2 to GAIN=1 by applying noise?

■Settings

・Using internal reference

・AVDD = 5V

■Conditions

・All channel shows half of expected voltage. For example from 2V to 1V.

・Power line is below and applied noise to 24V.

24V → 5V → AVDD

・Noise (IEC61000)

Frequency from 90~130MHz (Frequency increases 1.01 times every 1 second)

Noise level 4V

time: 60 sec

Best Regards,

ttd