Tool/software: Code Composer Studio

Hi,

I have a problem using ads1292.

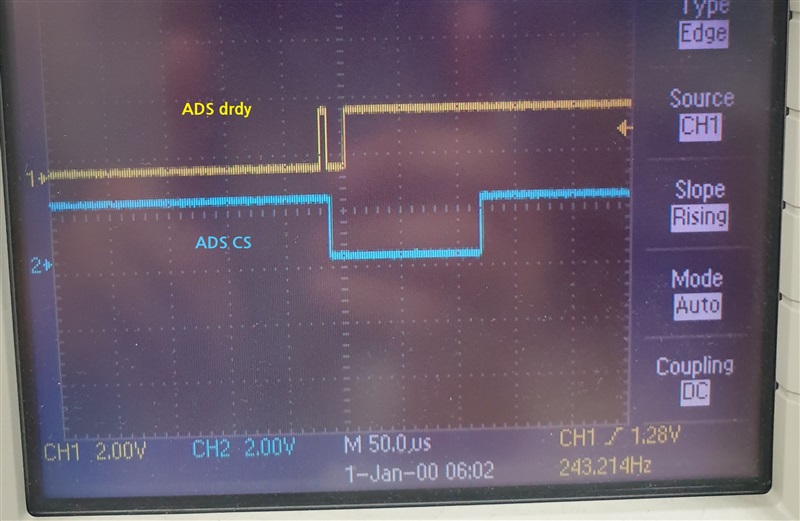

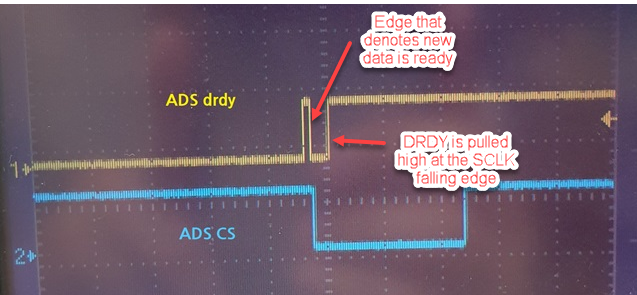

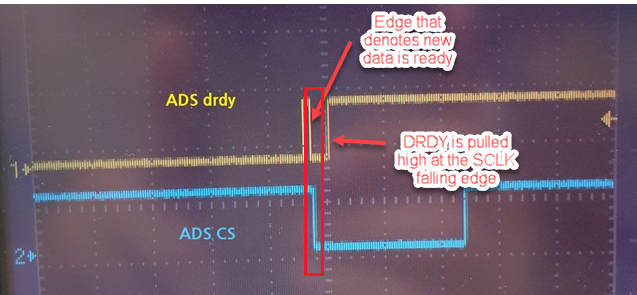

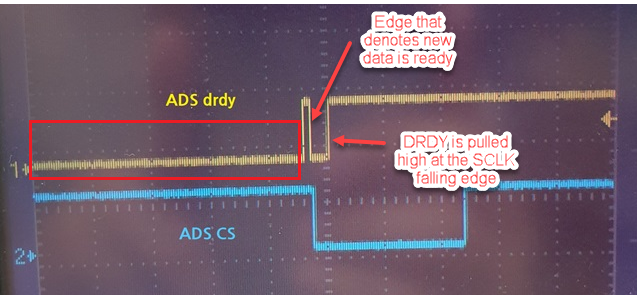

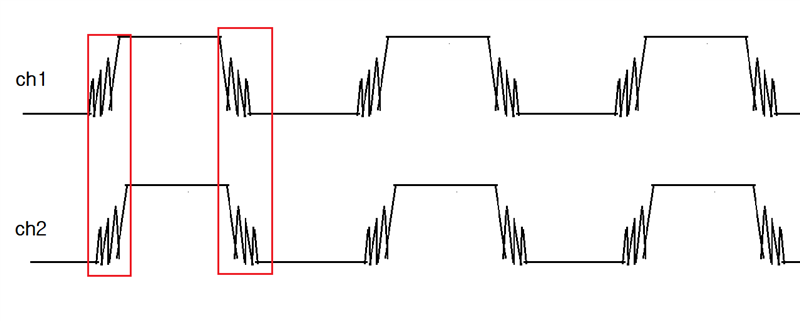

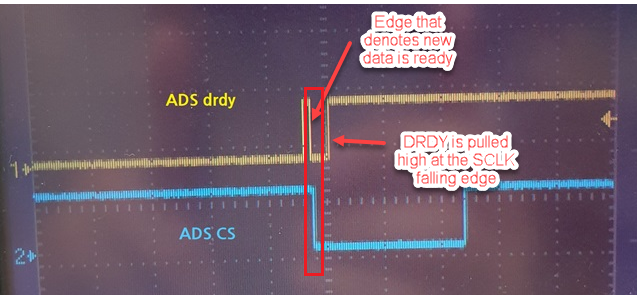

When i read sample using continuous mode, drdy pin of ads state is abnormal.

(interrupt edge is low to high : raising edge)

Does anyone know about these problem?

This is my code.

int main(void)

{

WDT_A_hold(WDT_A_BASE);

init_CS();

init_GPIO();

//GPIO_setAsPeripheralModuleFunctionOutputPin(GPIO_PORT_PJ, GPIO_PIN2 | GPIO_PIN1 | GPIO_PIN0, GPIO_PRIMARY_MODULE_FUNCTION);

register_mainOperation(main_idle);

__enable_interrupt();

initUart();

initUserPort();

setPowerEnPin(true);

initADS1292();

hal_ads_start();

read_started = 1;

while (1)

{

mainOperation();

if (ads_read_flag)

{

hal_ads_read_sample(ads_buff);

ads_read_flag = 0;

}

}

}

#pragma vector=PORT1_VECTOR

__interrupt void P1_ISR(void)

{

switch (__even_in_range(P1IV, P1IV_P1IFG7))

{

case P1IV_P1IFG1:

ads_read_flag = 1;

break;

case P1IV_P1IFG2:

afe_read_flag = 1;

break;

default:

break;

}

}

- ADS1292 SCLK : 1MHz

- ADS1292 CLK : 2MHz from msp430

And, this is register setting of ads1292.

0x01, //CONFIG1 : 4kSPS for single shot mode 0xF3, //CONFIG2 : enable Lead-off comparator, enable reference buffer, reference 4V 0x10, //LOFF 0x65, //Channel1 //power down 0x65, //Channel2 //gain12 0x25, //RLD_SENS 0x0F, //LOFF_SENS 0x40, //LOFF_STAT 0x02, //RESP1 0x03, //RESP2 0x03 //GPIO

Thanks.

Regards,

Youngjun