Customer is having issues reading from the Rx FIFOs over SPI when using the DAC8742H in HART mode, although they appear to be able send data to the Rx FIFOs and initiate a HART transmission.

In there system, the SPI clock is ~500kHz, and the gap between successive SPI frames is greater than 3usec. The SPI read request interval is 60usec, so this significantly exceeds the required minimum of 2.442 usec between SPI frames

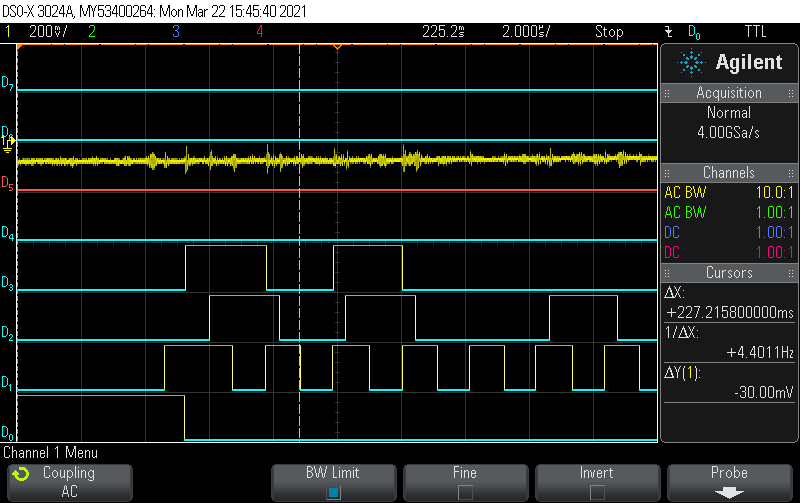

In there test code, They send two consecutive MODEM_STATUS read requests: 0xA00000

The response received during transmission of the 2nd read request is 0xA04044, indicating FIFO_M2D is FULL, and FIFO_D2M is EMPTY.

They send 4 consecutive FIFO_M2D Register read requests: 0xA40000

The responses received are:

0xA04044

0xA405FF

0xA405FF

0xA405FF

The first of the 4 is the response from the 2nd status read request.

The other 3 responses indicate FULL_FLAG and FIFO_LEVEL = 0. They suppose the FIFO_LEVEL has simply overflowed and can't represent a fill level of 16. However, why does the reported FIFO_LEVEL not decrement with each consecutive read request? Also, the HART data byte is always 0xff, regardless of how many bytes they try to read.