All:

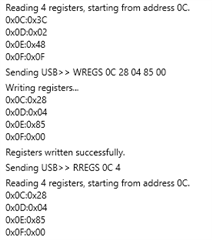

I am debugging WREGS, and I am not seeing the registers written.

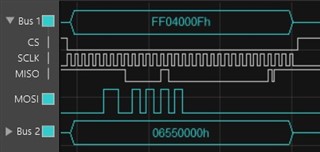

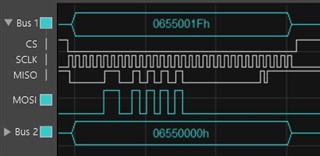

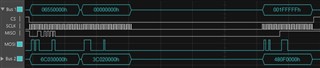

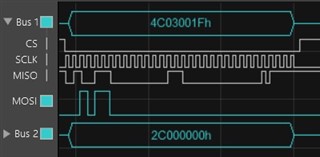

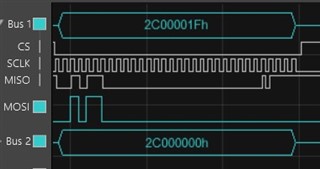

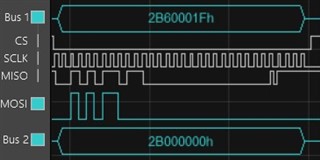

I have external 32-bit SPI running at 20 MHz, and I am sending the following, with CS active for entire 4 words:

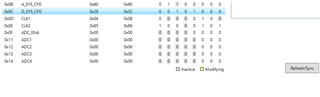

0x6C030000 (WREGS, starting at location 0xC, write 4 registers)

0x3C020000 (D_SYS_CFG = 3C, CLK1 = 02)

0x480F0000 (CLK2 = 48, EN_ADC = 0F)

0x00000000 (CRC not used)

However, when I do a single RREG of 0xC to read the contents, I get value of 0.

If I use single WREG command, I can write the proper values and read them back from the above registers.

I must be overlooking something - what am I doing wrong?