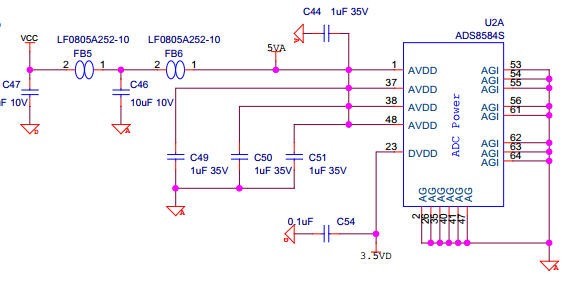

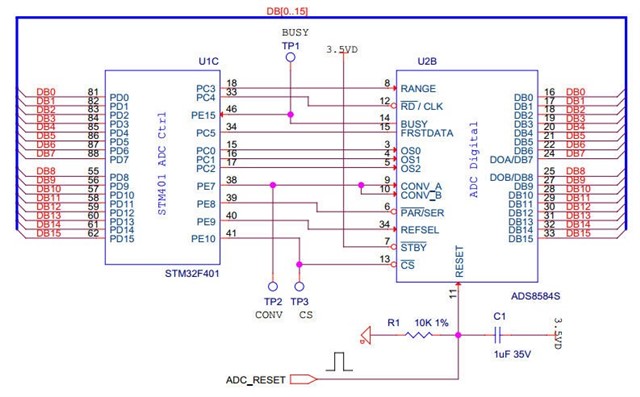

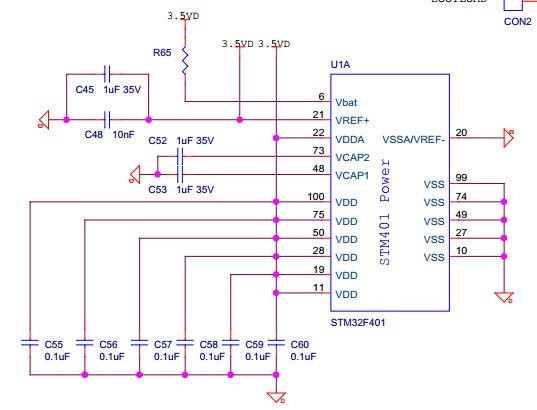

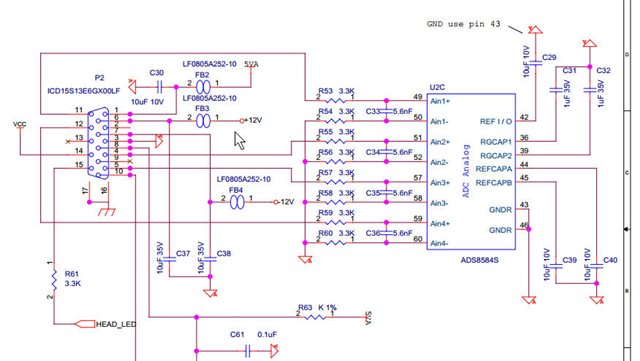

We use ADS8584S A/D converted in our project for analog measurements along with the STM32F401 MCU - the schematic design is attached

In our application the ADC is configured to work in parallel mode, +/-10V dynamic range, internal reference voltage of 10V, oversample between 0 and 4

Generally speaking the ADC works in the stable way with no missing code

We have several operation issues as explained hereunder:

1. BUSY signal - critical issue

--------------------------------------------------------------------------------

We use the threshold (MCU interrupt mode) to detect the start of conversion, after that to read the data from A/D

The high level of BUSY signal is approximately 1.7V, closed to MCU input threshold

To improve the threshold voltage we tried to add pull-up resistor between 20-3K, but the High level of the BUSY signal is not changed and is remained ~1.7V

Please, advise how to increase this signal voltage

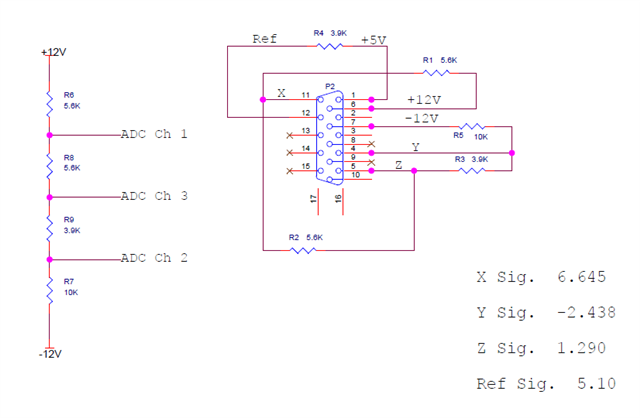

2. Voltage calculation - critical

-----------------------------------------------------------------------

We have about 20% deviation offset between the calculated value and supplied known voltage

For example:

- 597V supplied measured as 17,450 which means 5.325V

- -2.597V supplied measured as -6,483 which means -1.978V

The deviation is slightly not linear

Please, explain how to calculate the analog data from the digital values to receive precise values

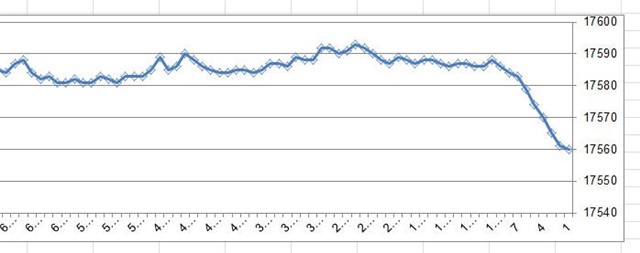

3. ADC in loop conversion - critical

------------------------------------------------------------------------

Running ADC conversion in loop with delay of 10 usec between each measurement, brings first 10-15 readings different from the rest of the of data. Delay of 10 sec and running again of the conversion in loop brings again about 10-15 not valid first readings. The data is presented on the graph attached

Please, explain how to fix it