Other Parts Discussed in Thread: LMH6552

Hello, I saw your question in the forum, and now I have the same problem as you.

https://e2e.ti.com/support/data-converters/f/73/t/660047

My main references: tidub15, tidubh9.

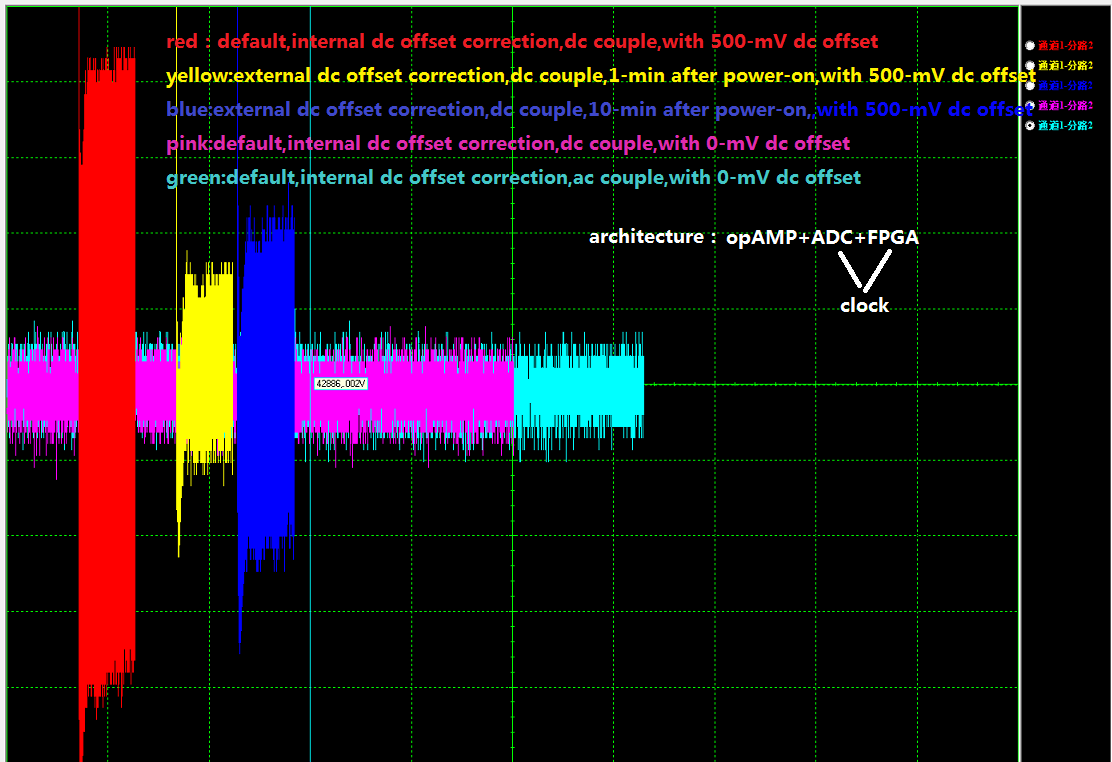

Hello, I am debugging the board of ADS54J60. PCB is drawn by myself. Using DC coupling mode and LMH6552 operational amplifier, which converted the single-ended signal into differential signal, which is supplied to ADS54J60 for sampling.

When the input signal is collected by ADC, problems are encountered at present. The problem is described as follows. When the input signal has no DC level component or the DC level component is very small, the sampling of ADS54J60 is normal. Once the DC level component in the signal is large, or the bias voltage is large, the ripple will occur. The ripple frequecy is 1/4 of the sampling clock frequency of ADC, and the ripple amplitude is 0-512, [8:0]. (Tests at 1GHz and 750MHz, respectively, yielded similar results)

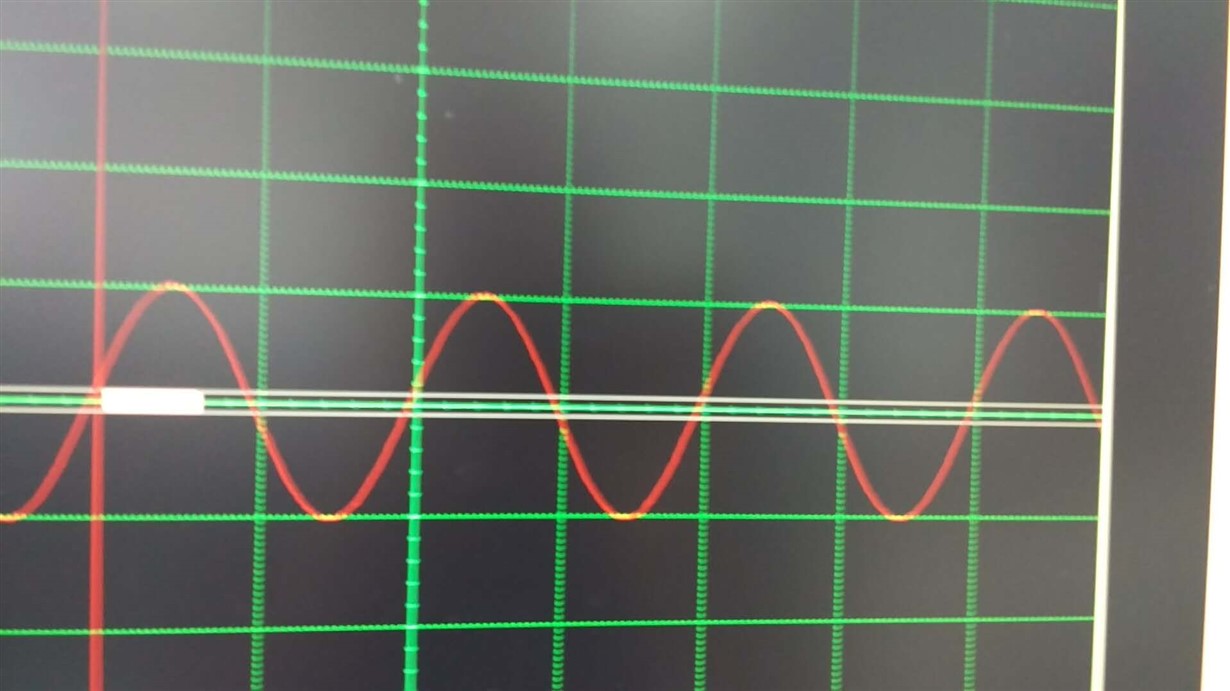

here followed the normal sampling waveform

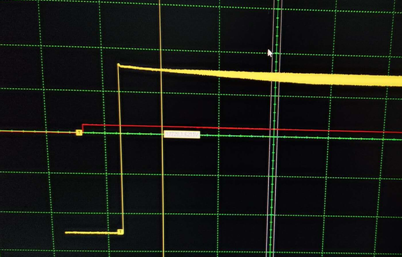

This is a process of ripple shock when the signal has a relatively large DC level component. Please note that the DC level component causes the onset of the earthquake. The time of shock stabilization is about 35us. as followed the ripple shock waveform

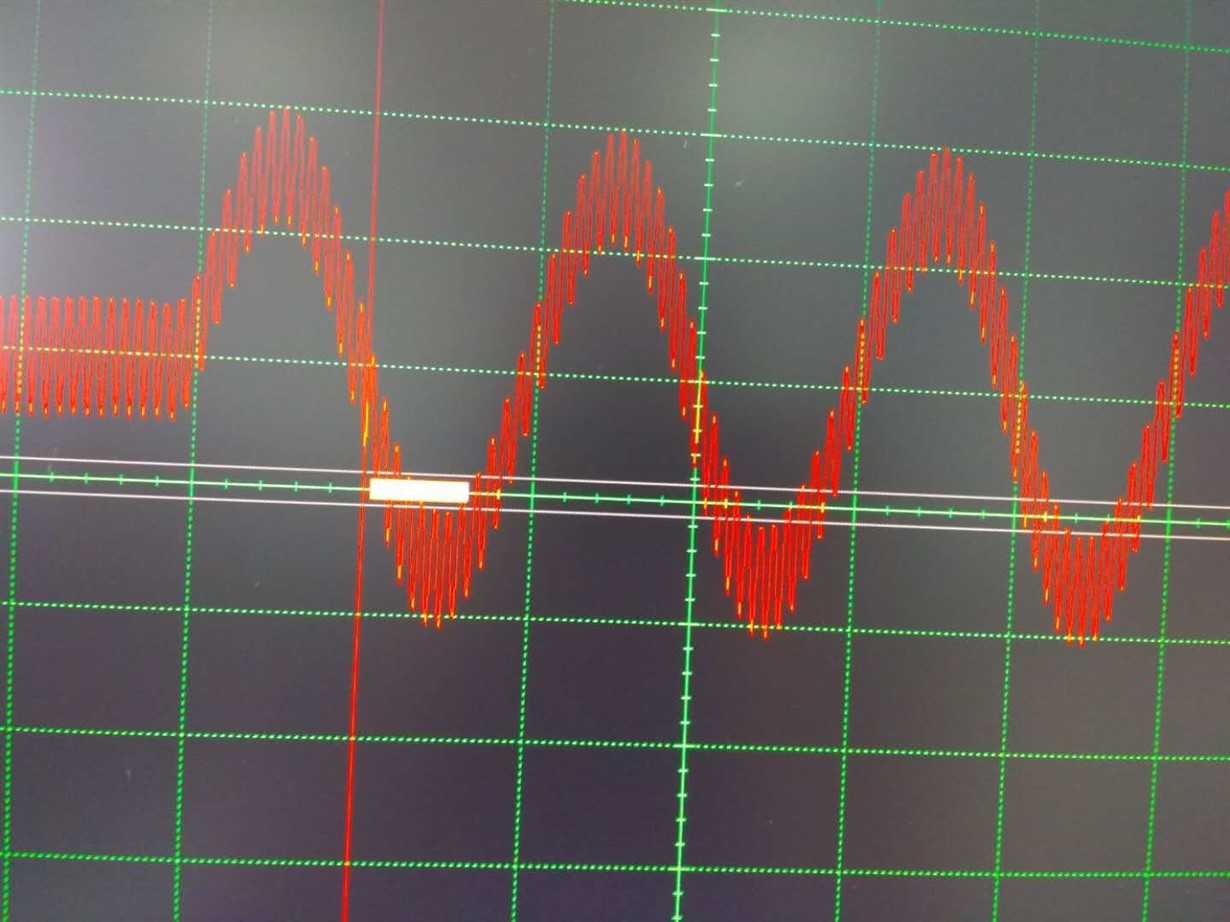

the detailed ripple waveform is followed

I found that the current ripple waveform amplitude has nothing to do with the waveform shape and waveform amplitude. The ripple frequency is 1/4 of the sampling clock frequency of ADC. It feels that it is not a problem on the analog signal conditioning link.

I got confused, help please~