Other Parts Discussed in Thread: TINA-TI

Tool/software: TINA-TI or Spice Models

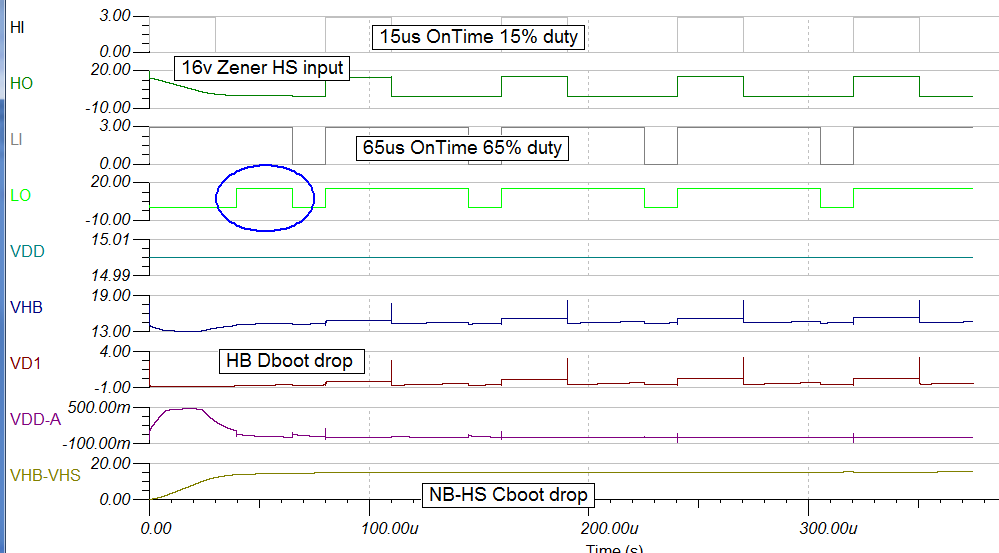

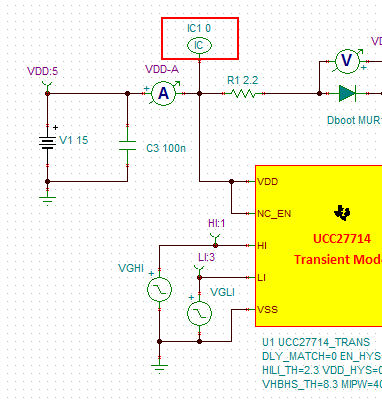

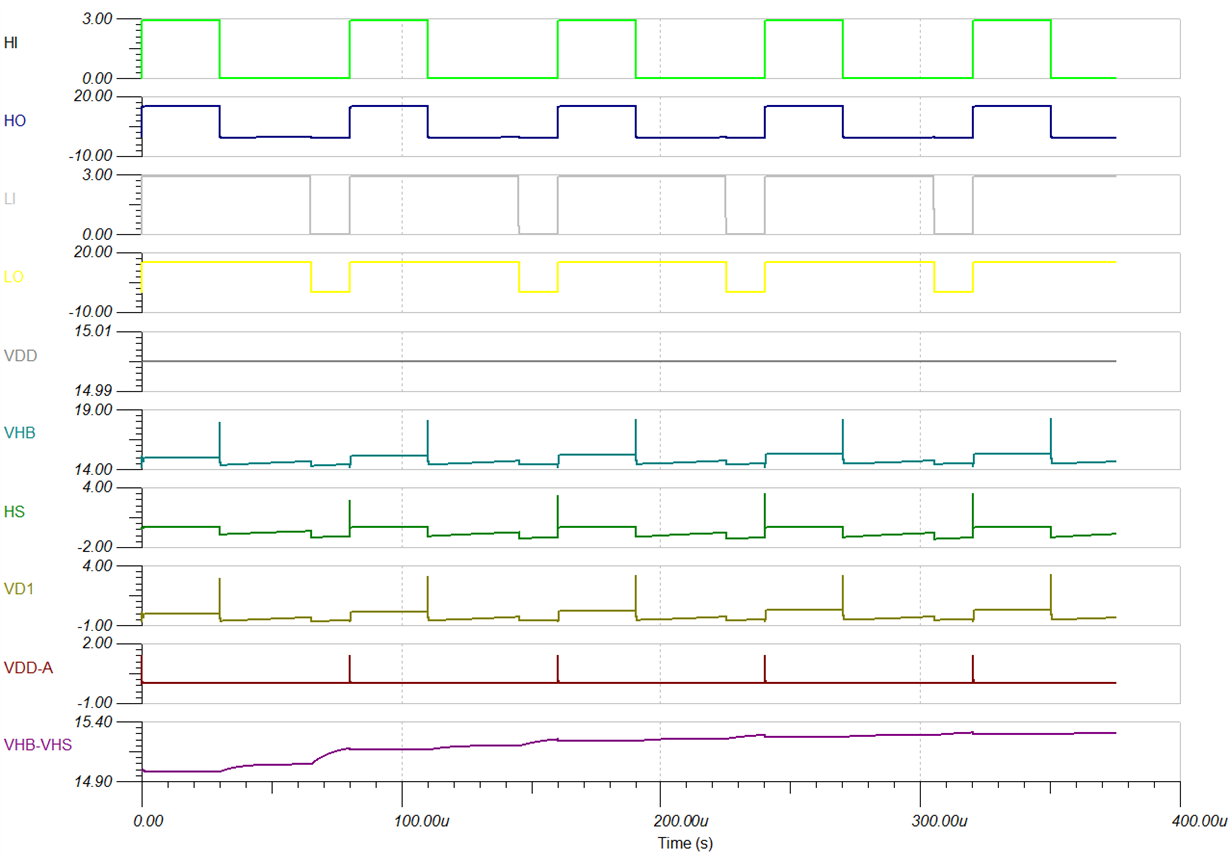

Issue of HS pin passing 1/2 bridge high voltage out the HO pin and compressing the HO signal in plot output when not arrested via added 16v zener on HS pin.

HS pin is connected to high side NFET source leading into drain at low side NFET, 1/2 bridge layout. Also have initial rouge pulse (blue oval) showing up in the LO output when 2 signal generators at different duty cycles are producing drive signals into HI/LI inputs, 80us period.

Is the HS pin passing high voltage out HO pin (+160v not shown) expected to occur in production chips?

Any idea what would cause the HO output to produce an initial rouge pulse as below capture shows?

Thanks,