- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

We encountered a similar problem when using the DMD DLP660TEVM and a DLPC4422 controller.

After using some different test patterns we can not get the dmd to display the connected external source correctly. The problem looks exaktly like described in the related question. We tried all proposed solutions, but none of them worked.

I hope we can resolve this issue.

Best Regards,

Florian

Florian -

I don't see any link or reference to the "similar problem" or "related question". Can you provide a link to the issue you are referring to, or describe the problem?

Thanks,

Gary

Florian,

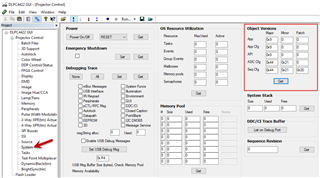

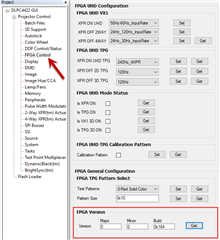

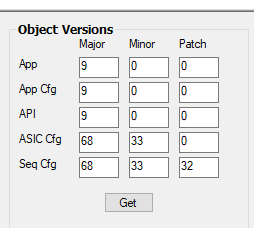

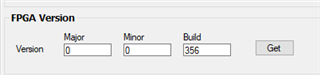

Can you confirm what versions of ASIC and FPGA firmware images are you running on the EVMs? You can find the ASIC firmware version under System and the FPGA firmware under FPGA Control.

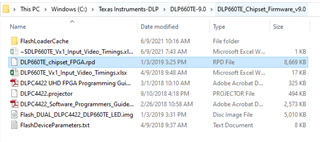

I would assume that you already loaded the ASIC and FPGA firmware that is provided with the firmware download from https://www.ti.com/tool/DLP660TE-SW. If that is not the case then please do so. ASIC firmware programming instructions can be found in the DLPLCRDC4422EVM User's Guide and the FPGA firmware programming instructions can be found in the directory created during firmware package installation (see below).

ASIC firmware version:

FPGA Firmware:

We downloaded and installed the firmware for the dlp660 provided by ti.com. Above you can find screenshots from our GUI.

Regards,

Florian

Florian,

We have tried to duplicate your findings with our setup and are not able to do so. Unfortunately we're not able to debug specific issues with Vx1 front ends that we haven't worked with, If you're working on designing a projector for production send me a friend request so that we can discuss offline on the best channels to get you setup.

Regards,

Mike

Our current goal with the dmd is not related to any projector work. We are just trying to use the dmd to display a binary pattern.

Do you have any suggestions on where the problem may lie? Since we get part of our videosignal displayed on the dmd, this should not be a Vx1 frontend problem or am I getting something wrong here?

Regards,

Florian

Florian,

I have sent you a friend request so that we can look into options offline.

Mike,

It seems like we are not the only customer with this kind of problem and turninig this discussion into an offline chat, would not benefit anyone of them. I would much rather keep this discussion online to also help others.

Do you have any other suggestions on how to resolve this issue?

Regards,

Florian.

Florian,

Are you using one of the specific timings supported w/ Vx1 pixel clock @ 600MHz? The supported timings are listed in an xls file included in the DLP660TE firmware and GUI package.

Regards,

Gary

| DLP660TE Recommended Video Timings for fixed 600Mhz pix clk, 8-channel Vx1 | ||||||||||||||

| Recommendations | H-Sync Parameters | V-Sync Parameters | ||||||||||||

| Resolution | Pixel Clock | H-Sync | V-Sync | H-Total | Display | Back-porch | Pulse-width | Front-porch | V-Total | Display | Back-porch | Pulse-width | Front-porch | |

| (unit:MHz) | (unit:KHz) | (unit:Hz) | unit:pixel | unit:pixel | unit:pixel | unit:pixel | unit:pixel | unit:Line | unit:line | unit:line | unit:line | unit:line | ||

| 1 | 3840x2160 | 600 | 110.95 | 50 | 5408 | 3840 | 256 | 32 | 1280 | 2216 | 2160 | 35 | 5 | 16 |

| 2 | 3840x2160 | 600 | 131.58 | 60 | 4560 | 3840 | 256 | 24 | 440 | 2193 | 2160 | 11 | 5 | 17 |

| 3 | 2712x1528 | 600 | 111.11 | 24 | 5400 | 2712 | 472 | 280 | 1936 | 4624 | 1528 | 49 | 6 | 3041 |

| 4 | 2712x1528 | 600 | 111.11 | 25 | 5400 | 2712 | 472 | 280 | 1936 | 4440 | 1528 | 49 | 6 | 2857 |

| 5 | 2712x1528 | 600 | 125 | 30 | 4800 | 2712 | 472 | 280 | 1336 | 4160 | 1528 | 32 | 6 | 2594 |

| 6 | 2712x1528 | 600 | 147.35 | 48 | 4072 | 2712 | 472 | 280 | 608 | 3070 | 1528 | 32 | 6 | 1504 |

| 7 | 2712x1528 | 600 | 150 | 50 | 4000 | 2712 | 472 | 280 | 536 | 3000 | 1528 | 32 | 6 | 1434 |

| 8 | 2712x1528 | 600 | 150 | 60 | 4000 | 2712 | 472 | 280 | 536 | 2500 | 1528 | 32 | 6 | 934 |

| 9 | 2712x1528 | 600 | 185.64 | 96 | 3232 | 2712 | 100 | 100 | 320 | 1933 | 1528 | 49 | 6 | 350 |

| 10 | 2712x1528 | 600 | 185.64 | 100 | 3232 | 2712 | 100 | 100 | 320 | 1856 | 1528 | 49 | 6 | 273 |

| 11 | 2712x1528 | 600 | 194.81 | 120 | 3080 | 2712 | 164 | 32 | 172 | 1620 | 1528 | 45 | 5 | 42 |

Gary,

we are currently using the settings row 8, but we also tried using row 7 with no difference in outcome.

Regards,

Florian

Florian,

There are 3 LEDs that might be somewhat helpful in maybe figuring out what is going on:

What is the status of these LEDs on your system when sending Vx1 data to the FPGA?

Thanks,

Gary

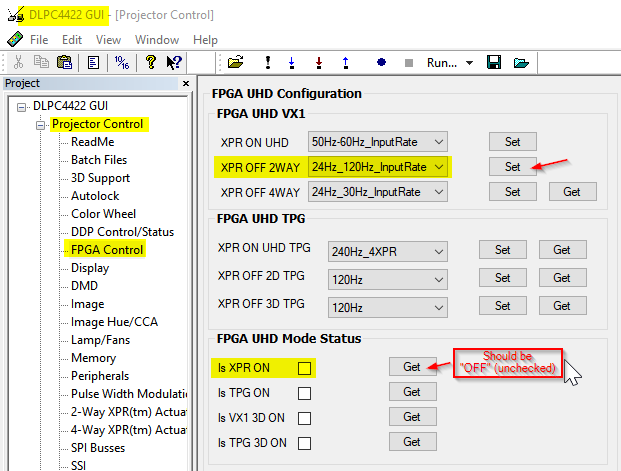

Florian,

Thanks. So, it seems the FPGA is configured (D10 is on), and there is a Vby1 Hot Plug Detect. For whatever reason, the Vby1 is not locking.

All of the rates in the table have been tested. I cannot recall if this is necessary to get a lock... but can you make sure the "XPR OFF 2WAY" is selected in the DLPC4422 GUI -> Projector Control -> FPGA Control...

Does that change anything for D1 (Vby1 Locked LED)?

Thanks,

Gary

Hello Gary,

thanks for your suggestion. Unfortunately, it did not change anything about the D1 LED status or the dmd image.

Regards,

Florian