Dear all:

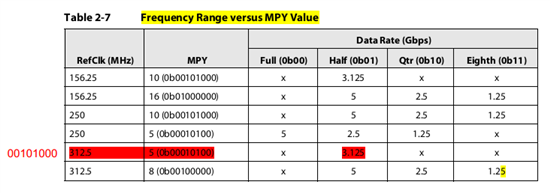

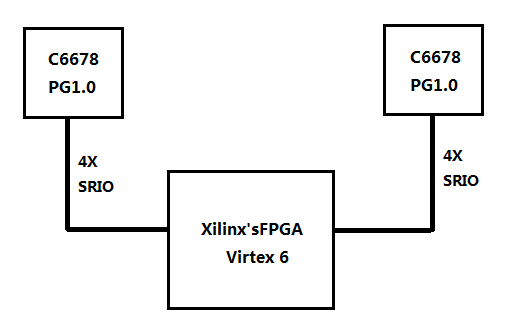

I am working to send data from C6678 to the Xilinx's FPGA(Virtex6) in my own board.The SRIO is configured as 4x3.125G.

There are two C6678s and one Virtex6 in the board, they are connected through the 4X SRIO. I can send data from FPGA to DSP or DSP to FPGA, and the data is all correct. But we meet a very strange problem.

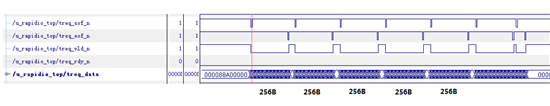

I send 1600 bytes from DSP to FPGA. In normal state, when i writed the LSU regs such as DestID, RapidIO address, DSP local address, Byte_count, DSP will send the 1600 bytes as 7 packets, FPGA should receive the 7 packets as well. The chipscope printscreen is below.

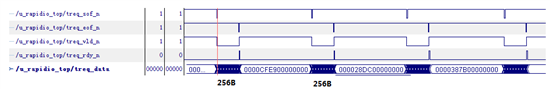

We use the same functions(FPGA and DSP), Sometimes, FPGA receive the 7 packets unsequentially. The chipscope printscreen is below. This is not a normal state. But i don't konw where is wrong. SWRITE or NWRITE was tested. Sometimes correct, Sometimes wrong. we check the FPGA, we find that FPGA's and DSP's SRIO Link changed to 1X. If i configure the DSP in 4X mode, it can change to 1X???

Another question, the table is right?

Thank you all!!!!