I have disabled the unused internal EMIF feature:

*(Uint32*)0x20C00008 |= 0x80000000; // Disable unused internal EMIF feature

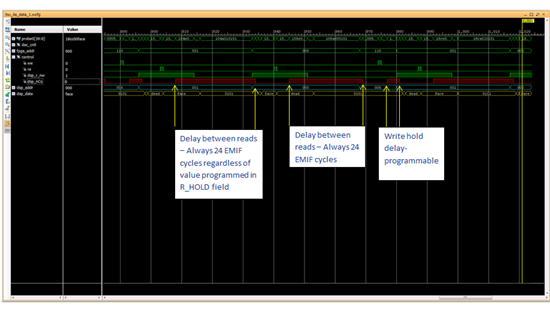

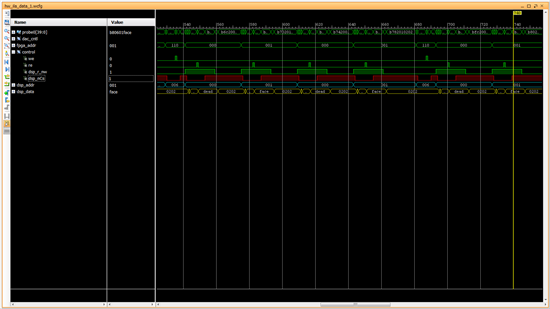

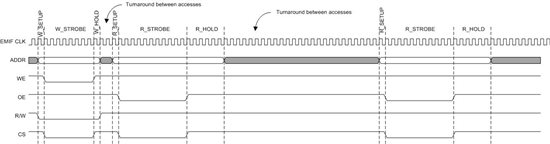

The W_SETUP, W_STROBE, W_HOLD, R_SETUP, and R_STROBE register fields NOW all function as advertised. However, no matter what value the R_HOLD field is programmed with, the R_HOLD period is always the "magical" 24 EMIF cycles.

Extended wait mode is disabled.

AWCCR = 0xC0000000;

A4CR = 0x80700551;

Would appreciate some advice.