Other Parts Discussed in Thread: SYSBIOS, OMAPL138, TMS320C6678

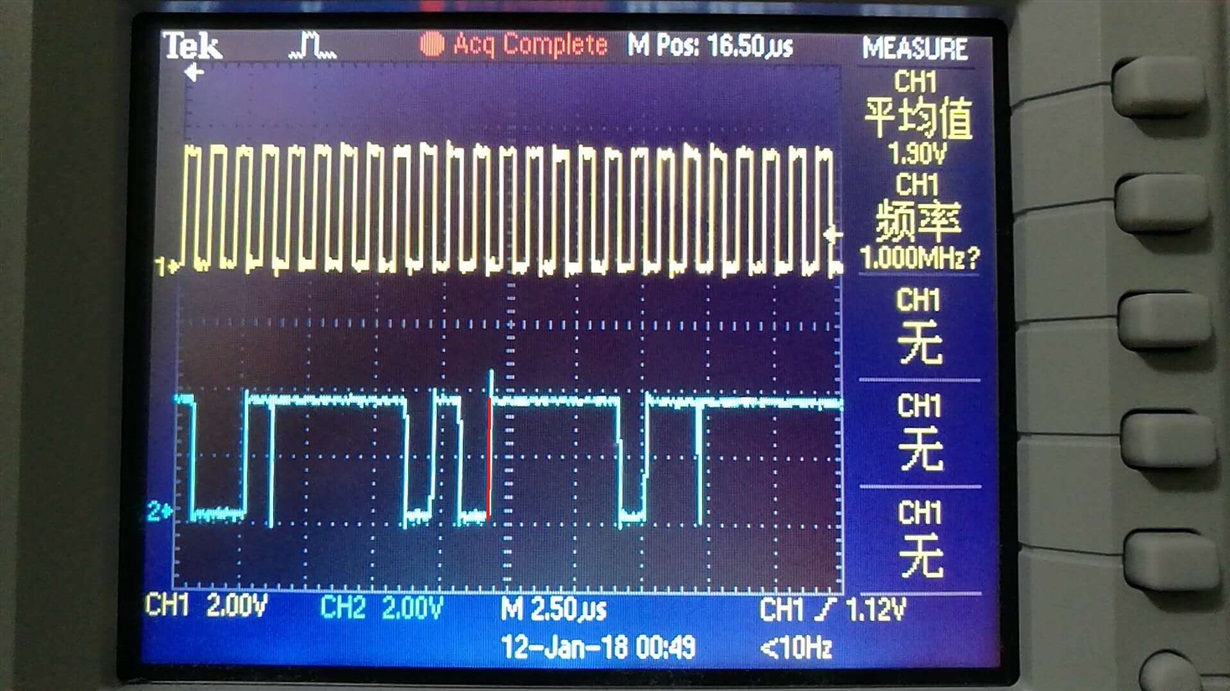

In my system, I use a MCU to communicate with C6748 throught SPI bus. The MCU is SPI Master, and the C6748 is SPI Slave.

The SPI_CLK is 10MHz, POLARITY = 0 and PHASE = 1.

I use C6748 EDMA to drive the SPI SOMI output.

For test, I let the C6748 to output 0xF1F2F3F4F5F6F7

For SPI_CLK= 4MHz, the read data is always right, which is 0xF1F2F3F4F5F6F7.

For SPI_CLK=10MHz, the read data is sometimes right, but sometimes wrong.

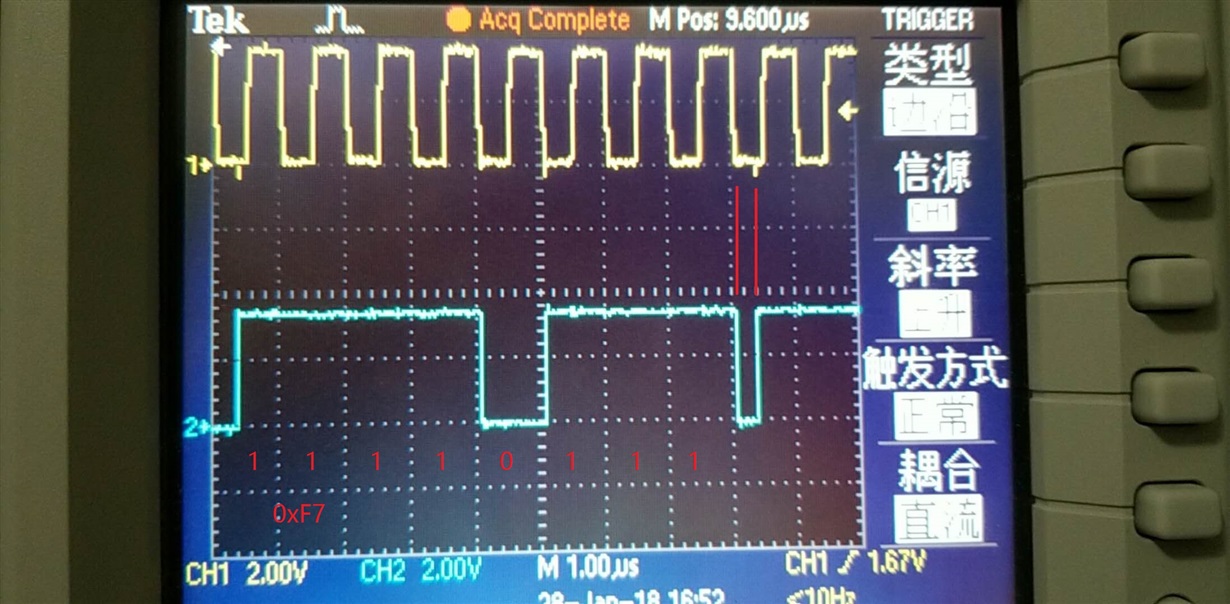

The wrong data is:

Read: 0xF1727374757677

Read: 0xF17273F4757677

Read: 0xF1F273F475F677

Read: 0xF1727374F5F677

.......

At first, I thought maybe the POLARITY and PHASE maybe wrong at the two end. But I've checked that they are alright.

And if the POLARITY and PHASE is wrong, the result should be one bit shift.

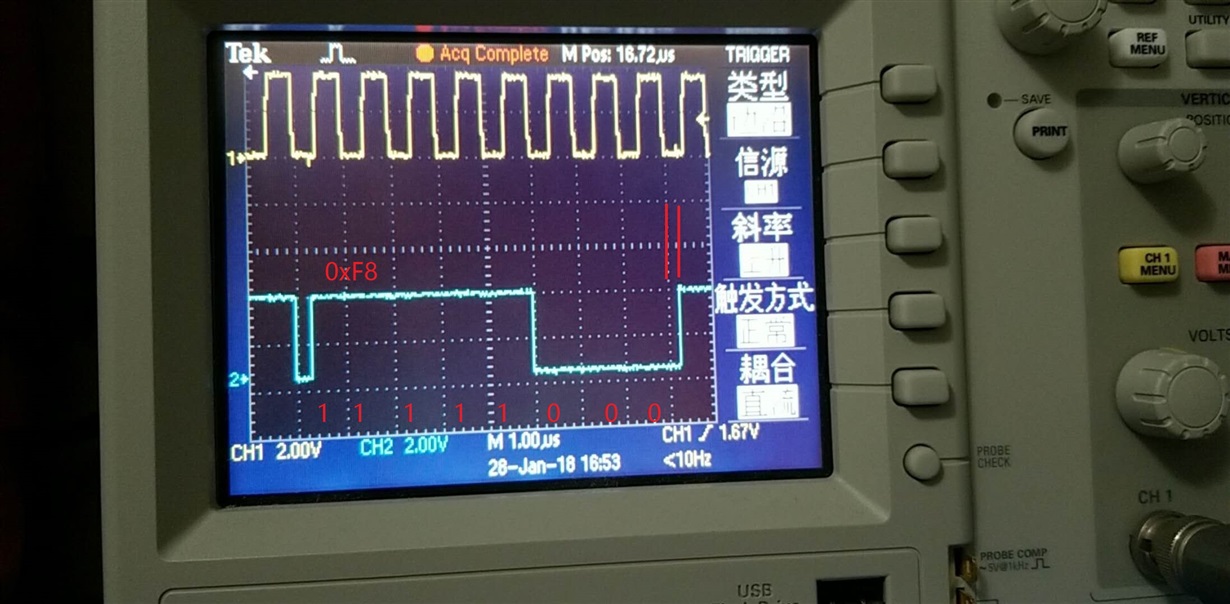

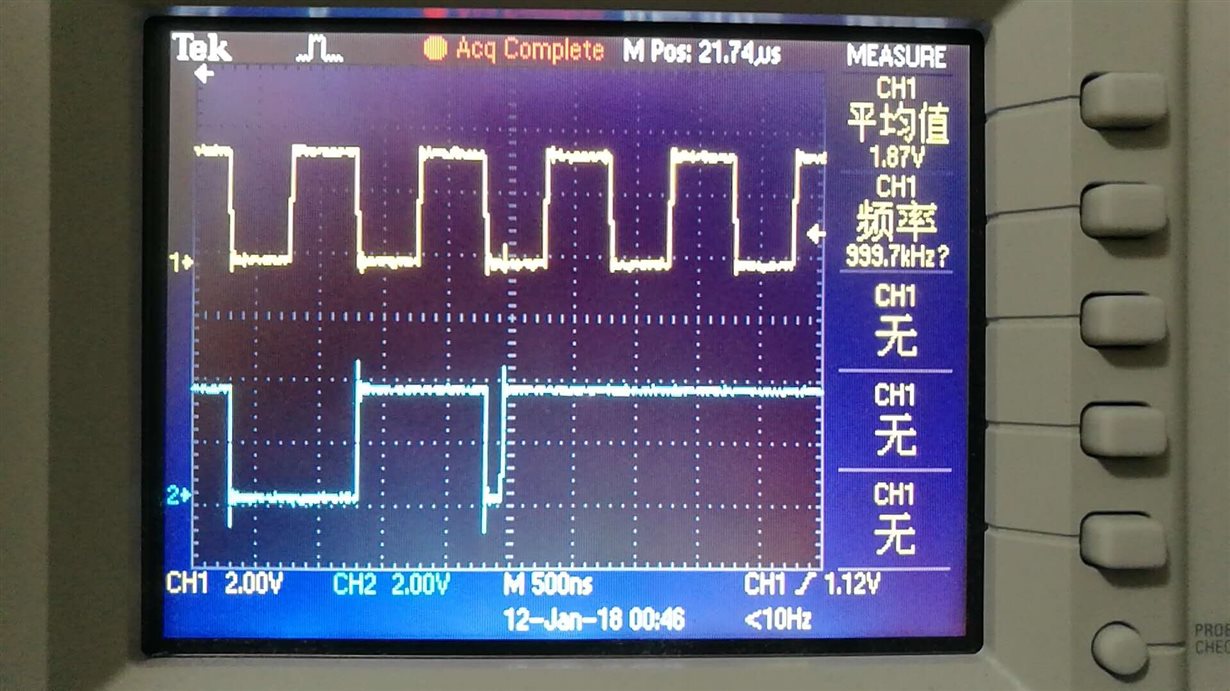

But you can see that, the wrong bit always happens to be the 1st bit of a whole byte!

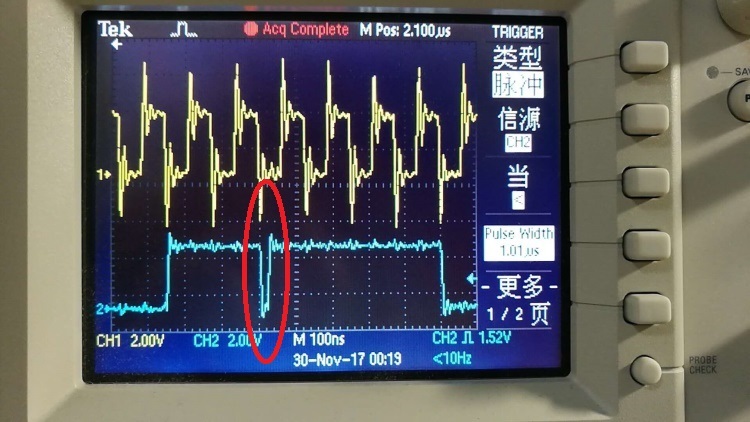

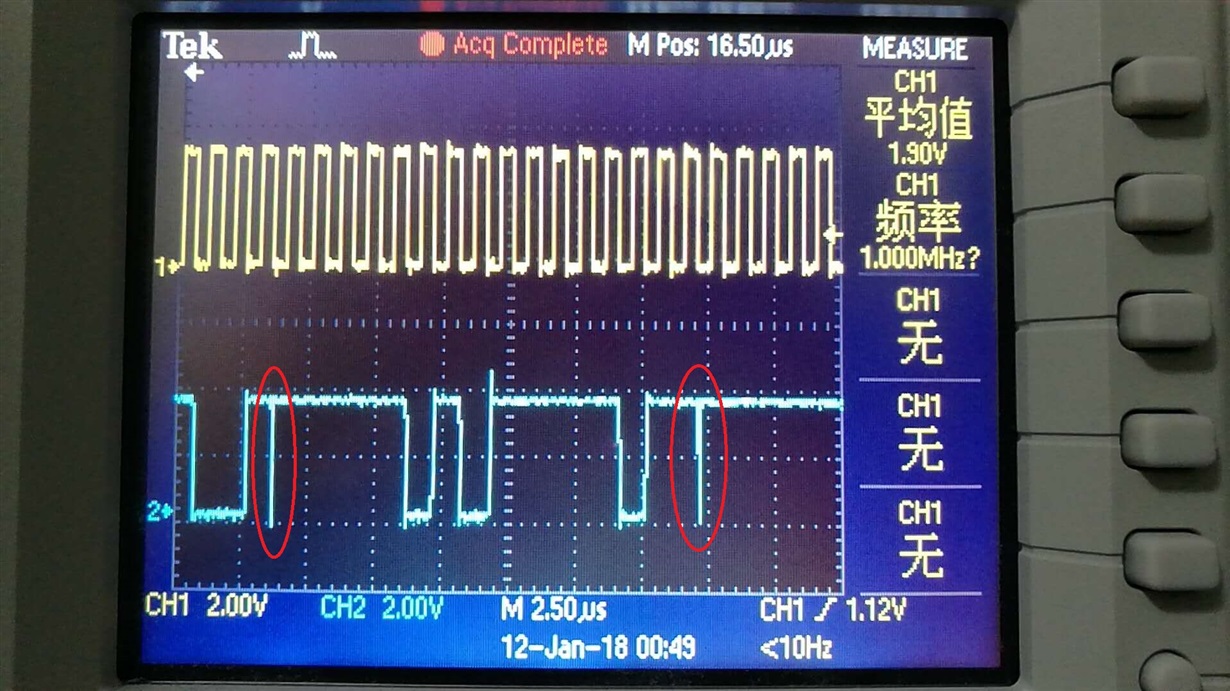

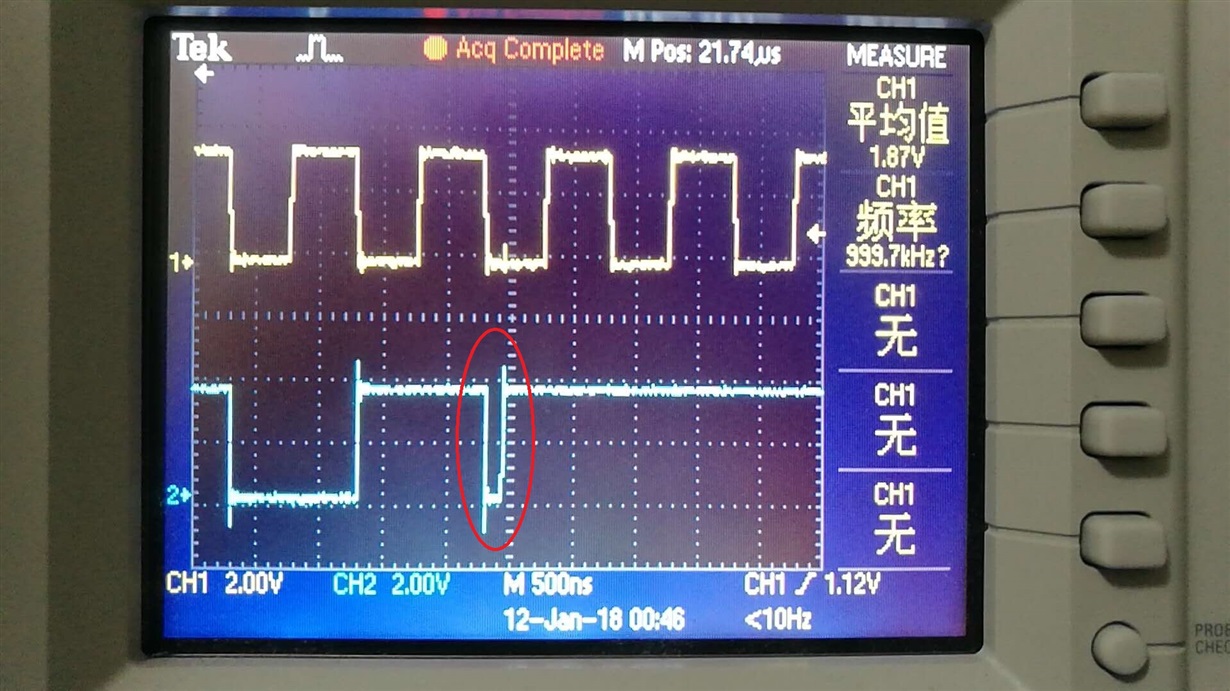

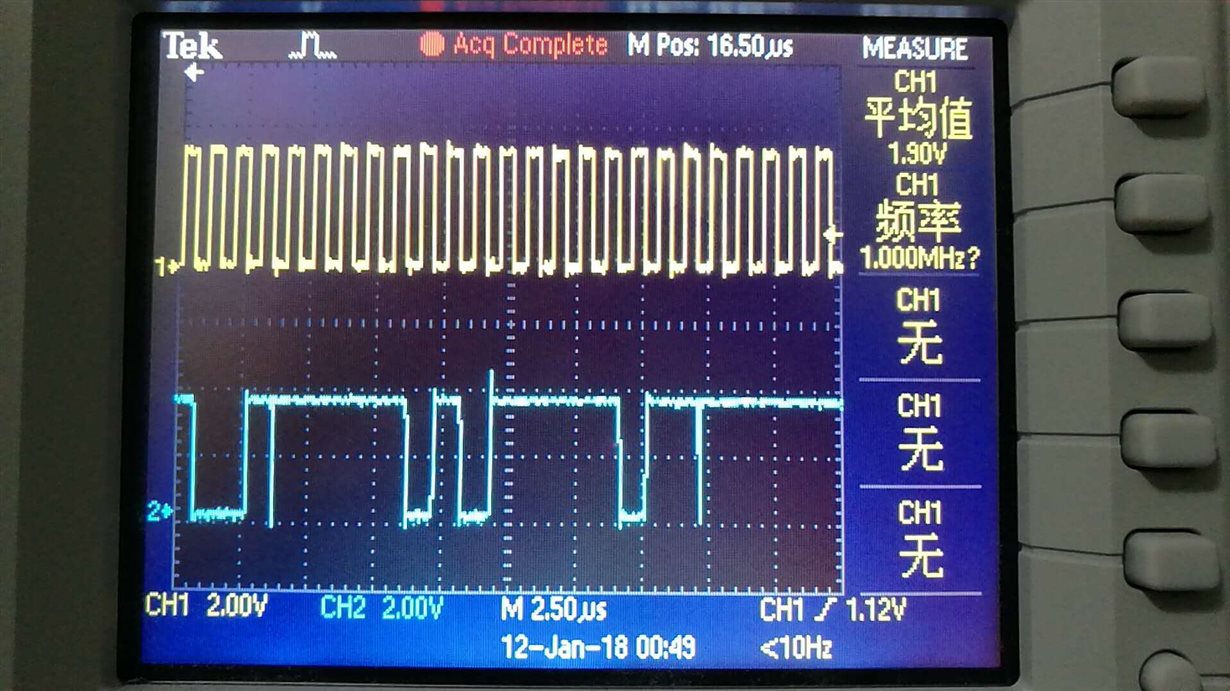

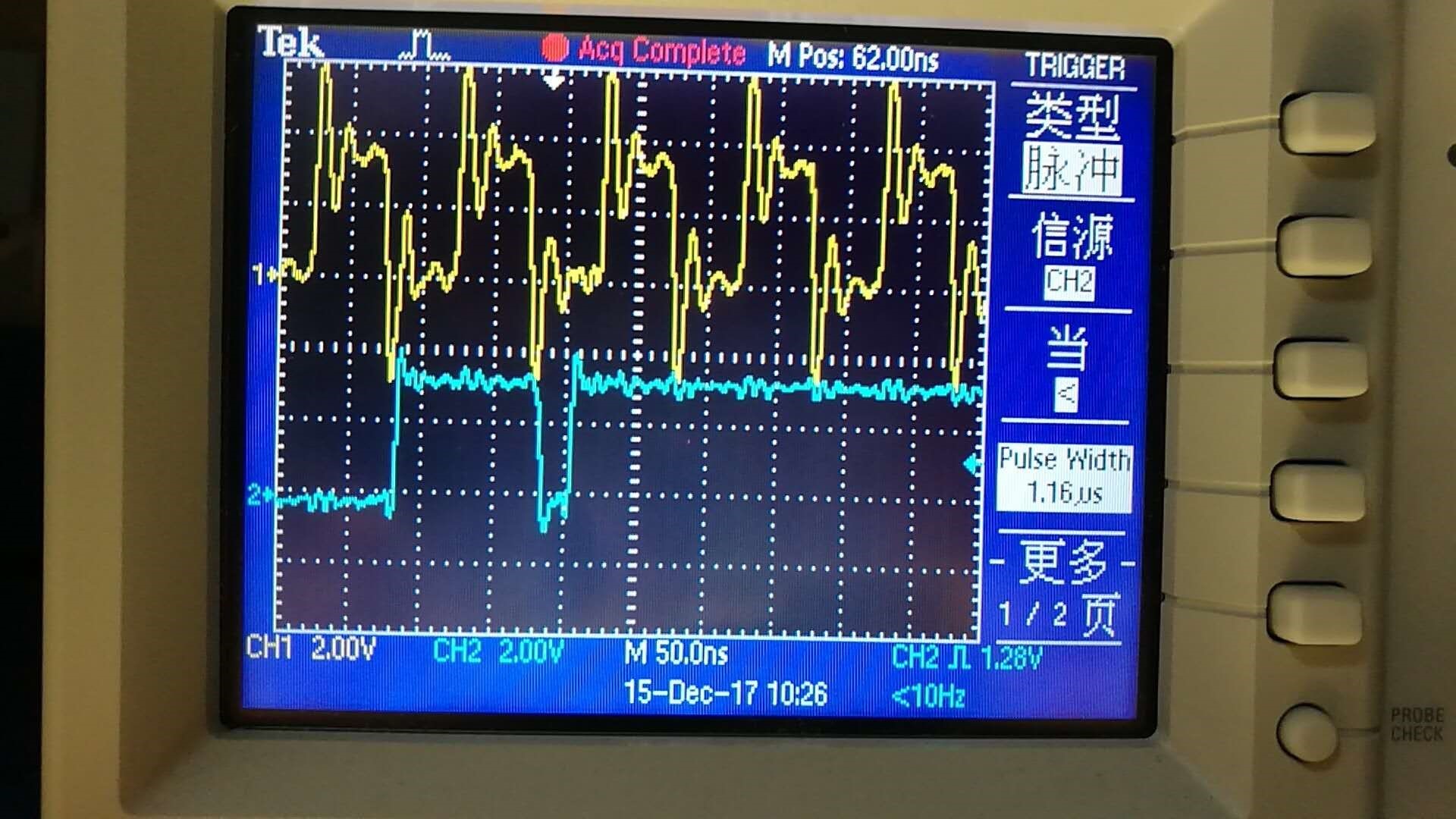

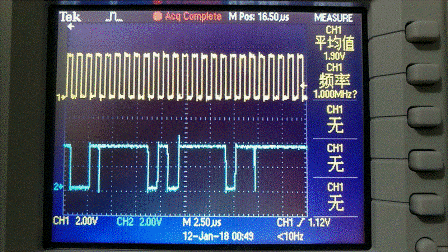

The waveform tells the truth:

This is a waveform between 0xF3 and 0xF4, there is a negtive pulse between the two bytes.

I think this is why my readata is wrong.

Question: Why there is a negtive pulse between the two bytes?