Hi Team,

Please advise me on a question bellow.

I am using DS1100DF410 connecting to an optical module.

During the system test, DS110DF410 report poor eye opening, when I referred address 0x27 and 0x28,

resulting excessive error on the output of the device.

It seemed to be that CTLE and DFE adaptation may not be completed in good condition.

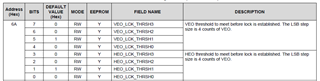

So, in order to fix this problem, I tried to tune HEO VDO threshold from default 0x44 to 0xCC

in address 0x6a, while set bit 7 to '1' in address 0x3E (Default value is also '1')

However, DS110DF410 still show lock despite of small vale of HEO VEO in address 0x27 and 0x28.

I suspect that HEO VEO threshold may be ignored.

Q1. Can you let me know if it is true that DS110DF410 make de-assert LOCK if either VEO or HEO

is lower than the threshold?

Q2. Can you le me know the proper procedure wen you use HEO VDO threshold?

Q3. Can you proof above procedure using EVM?

Q4. Dose DS110DF410 refer HEO VEO only lock process, or after establish lock too?

Q5. The HEO and VEO values are 6 bits, while HEO VEO thresholds are 4 bits.

How VEO/HEO and thresholds related?

Q6. When Disable HEO/VEO lock monitoring by clearing bit 7 in address 0x3E, the auto adaptation of

CTEL and DFE are still effective or not?

Mita