Dear Expert

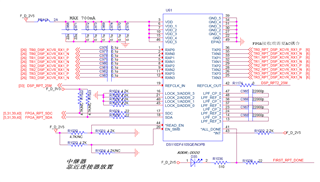

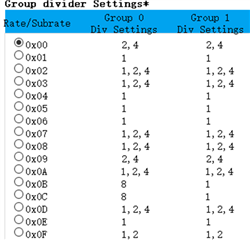

Set it up as shown in the figure below.The rate of input data stream is 4.8Gbps and the signal quality is good.But the repeater cannot be locked at 4.8G.With oscilloscope observation, it can be locked at 4.8G.Would you like to ask what may be the cause?