Part Number: SN65DP159

Other Parts Discussed in Thread: TUSB3410, TUSB3410UARTPDK

Issue:

- Unable to get video output on sink device from retimers when GPU resolution is set to 3840x2160@60 (HDMI 2.0 resolutions in general).

What works:

- Resolutions up to 4096x2160@30 (all HDMI1.4 resolutions).

What we have tried/verified:

- We have verified that the retimer's functional mode and TMDS clock ratio is being setup correctly for HDMI 2.0 data rates.

- We have verify with our scope that the data and clock signals are present at the expected voltage levels.

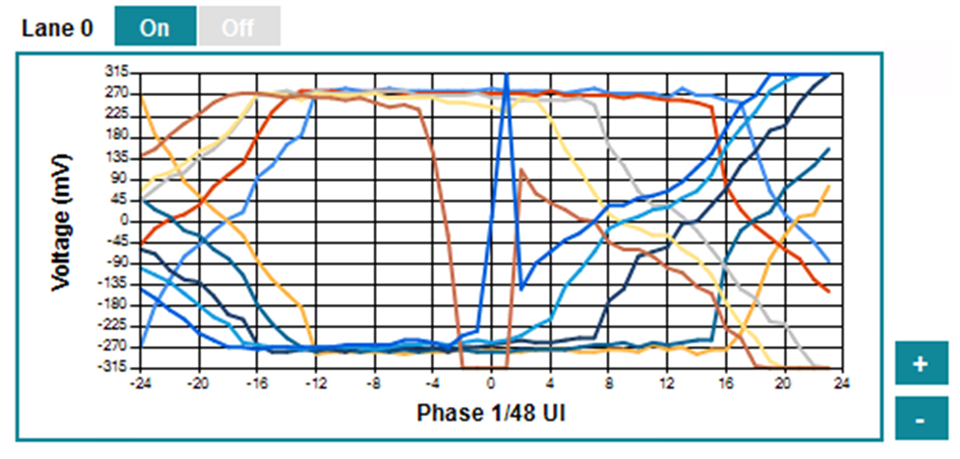

- We have been able to tune the retimers to the point that we are passing HDMI 2.0 eye mask compliance test even though there is still no video present.

- The scope is unable to complete interpair skew measurements because it can't find sync patterns in the data lanes.

Current Theory:

- We believe the channel between the GPU and Retimer is the issue. We believe the default GPU settings intended for a port and cable is overdriving the channel when used with our 2 inches of trace between the GPU and retimers. We think this is causing the retimers to output corrupted data with a well shaped eye.

- We have changed the GPU Vswing and de-emphasis levels attempting to improve the channel between the GPU and retimers. Without some type of feedback here, we are turning knobs without being able to verify whether we are improving things or not.

- We think the default retimer equalization settings would be correct for this setup but we are open to your input on this.

- Our next planned steps is to use the TI USB to I2C adaptor to try and characterize the channel between the GPU and Retimer (could you help us identify the part number for this adaptor?)

- Is this the best next step considering that we are currently unable to get a video stream at 4k 60 on the sink device? EyeScan tool users guide seems to imply that this only works with a functional channel.

- Any other ideas/suggestions on how to further debug this problem are welcome.

4k 60hz eye mask