Other Parts Discussed in Thread: ALP

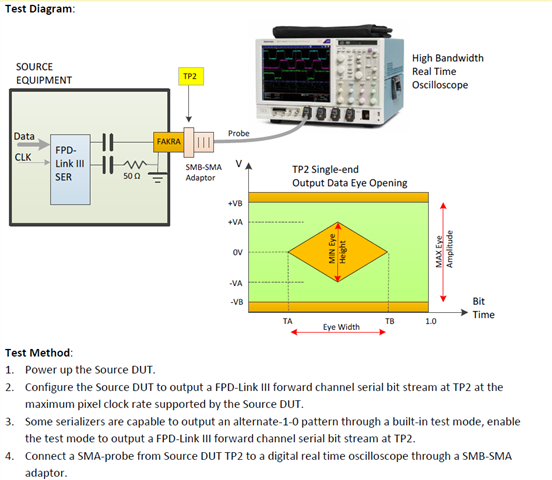

I am looking to perform the specific steps mentioned in the referenced image. Can you please comment if the DS90UB953 can be configured for this?

Once connected to the scope, how can I control the line rate of the DS90UB953 ? I would like to analyze at the maximum speed of 4.16Gbps.

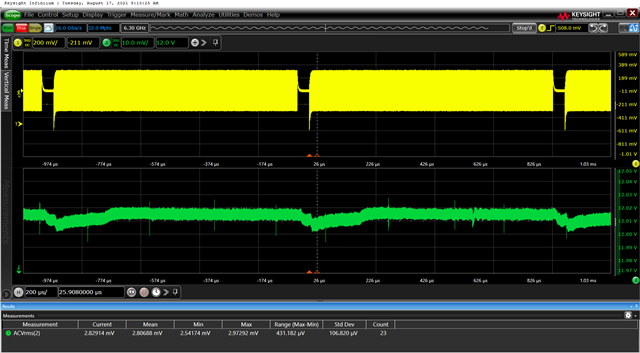

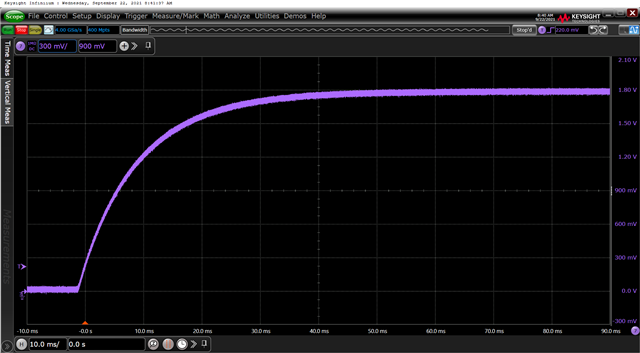

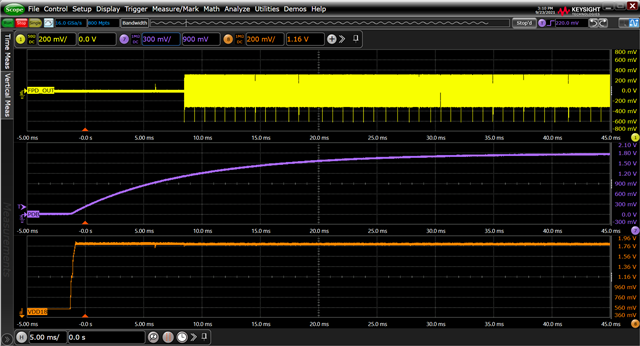

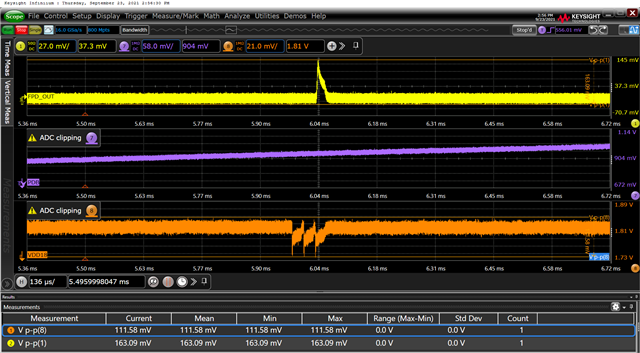

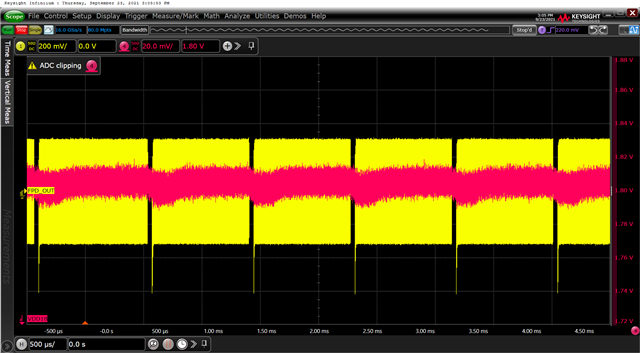

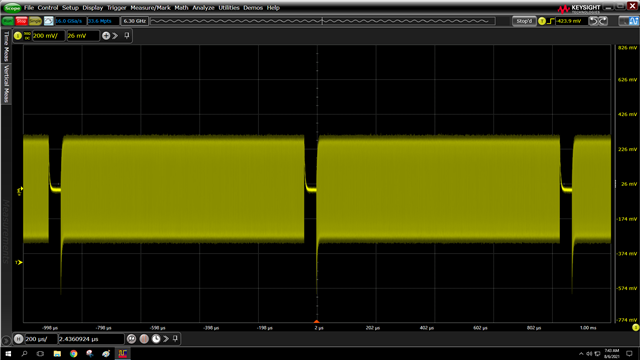

In the same configuration as pictured above (i.e. SER terminated into scope) I notice that every ~1ms, the serializer goes to electrical idle. There is an RC time constant before the signal is back to nominal levels. Is there a way to force continuous output and avoid electrical idle?

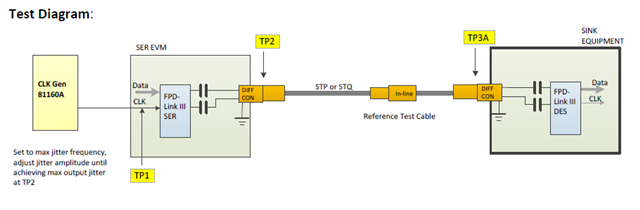

Where do I connect the 81160A on the SER EVM to perform the following test? There is no connector on the board where TP1 is screen printed.

thank you!

-Kevin Kershner