Dear team,

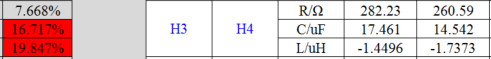

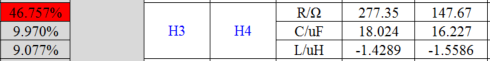

My customer uses this device for USB 2.0 interface. H3 and H4 are two USB pins. The CAR OEM has a requirement that they need to test LCR of USB signal pin before and after ESD test(power down mode), and then make sure the difference is smaller than 10%. But our device can't meet 10% requirement. I want to confirm with you whether 10% requirement is reasonable. Have we did such test? Do we have a range for LCD fluctuation?

Thanks & Best Regards,

Sherry