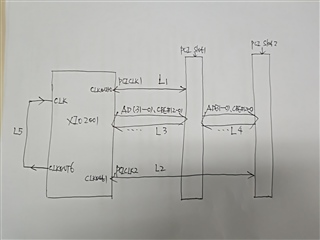

1、Should the routing length of the clock signal pciclk1 connected to PCI slot 1 by xio2001 be equal to that of the clock signal pciclk2 connected to PCI slot 2 by xio2001?

2、Do the signals in PCI slot 1 that are synchronized with the clock signal pciclk1, such as the signal of ad31-0, have the same length?

3、Fbclk routing length requirements?

4、Is the clock signal pciclk of PCI slot 2.5 inches shorter than the length of ad32-0 signal?

thank you