Part Number: SN75LVDS387

Hello,

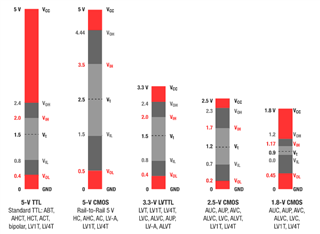

I want to provide a single-ended signal from an Intel Cyclone 10 GX FPGA to SN75LVDS387 and the signal is 2.5 LVCMOS rather than LVTTL.

The FPGA does also output 3.0 LVTTL, but the available pins are much less and do not meet our requirements.

The SN75LVDS387 datasheet does not seem to explicitly list LVCMOS input support, but hints it.

So is it supported?

Thank you