Hi team,

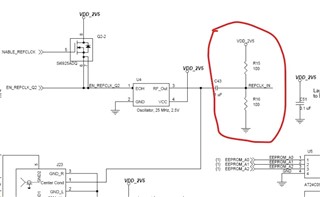

May I ask why capacitive isolation is required in the above figure?

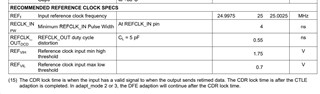

After the resistance 100 ohms, 2.5V is divided into 1.75V, but the high Viet threshold is also specified as 1.75V in the datasheet, if there is a safety issue with this critical voltage?

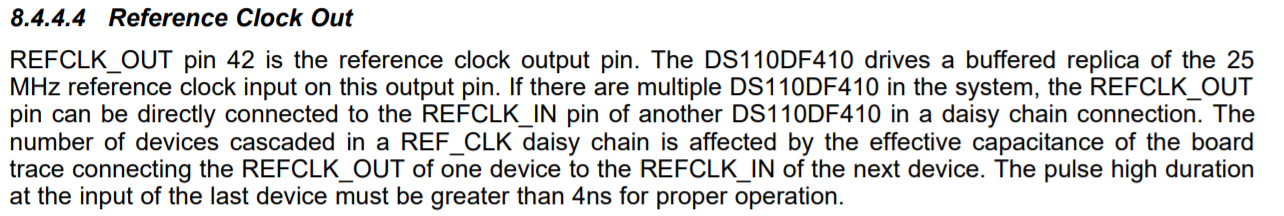

If the customer has to use a clock Daisy chain design, the REFCLK_out of A connect to B’s REFCLK_in.

Do they also need to add a capacitor similar to this, also pulling up and down two 100 ohm resistors?

Thanks!

Regards,

Ivy